Hi Team,

I am having a hard time with SPI communication. From datasheet of ADS1248 what I understood is that as long as I send clocks in multiple of eight I can send data back to back. But what I am experiencing is that I need to wait for approximately 20 micro seconds between each transfer. Any delay less than 20 microseconds resulting in communication failure. Is this delay is required? I haven't seen anything like that in datasheet.

SpiaRegs.SPITXBUF = 0x1640; // Send the SDATAC command and WREG Command 1st byte

DELAY_US(20);

SpiaRegs.SPITXBUF = 0x030A; // WREG Command 2nd byte and MUX0 register value

DELAY_US(20);

SpiaRegs.SPITXBUF = 0x0020; // VBIAS register value and MUX1 register value

DELAY_US(20);

SpiaRegs.SPITXBUF = 0x404A; // SYS0 register and WREG 1st command byte

DELAY_US(20);

SpiaRegs.SPITXBUF = 0x0105; // WREG 2nd command byte and IDAC0 register value

DELAY_US(20);

SpiaRegs.SPITXBUF = 0x03FF; // IDAC1 register value and NOP command

DELAY_US(20);

SpiaRegs.SPITXBUF = 0xFF04; // NOP command and ADC SYNC

DELAY_US(2);

GpioDataRegs.GPASET.bit.GPIO14 = 1; // Clear CS/ pin to HIGH

DELAY_US(201000);

// Reading conversion result of input channel 1

GpioDataRegs.GPACLEAR.bit.GPIO14 = 1; // Clear CS/ pin to LOW

r1 = 0x00000000;

r2 = 0x0000;

r3 = 0x0000000;

SpiaRegs.SPITXBUF = 0xFF12; // NOP and RDATA

DELAY_US(20);

SpiaRegs.SPITXBUF = 0x4000; // WREG Command 1st byte and 2nd byte

DELAY_US(20);

r1 = SpiaRegs.SPIRXBUF; // first 16 bits of conversion result MSB first

SpiaRegs.SPITXBUF = 0x254B; // MUX0 register value and WREG Command 1st byte

DELAY_US(20);

r2 = SpiaRegs.SPIRXBUF; // Second 8 bits of conversion result and remaining 8 bits of junk value

r3 += (r1 << 8) + (r2 >> 8);

DELAY_US(20);

SpiaRegs.SPITXBUF = 0x00AB; // WREG Command 2nd byte IDAC0 register value

DELAY_US(20);

SpiaRegs.SPITXBUF = 0xFF04; // NOP and SYNC command

DELAY_US(2);

GpioDataRegs.GPASET.bit.GPIO14 = 1; // Clear CS/ pin to HIGH

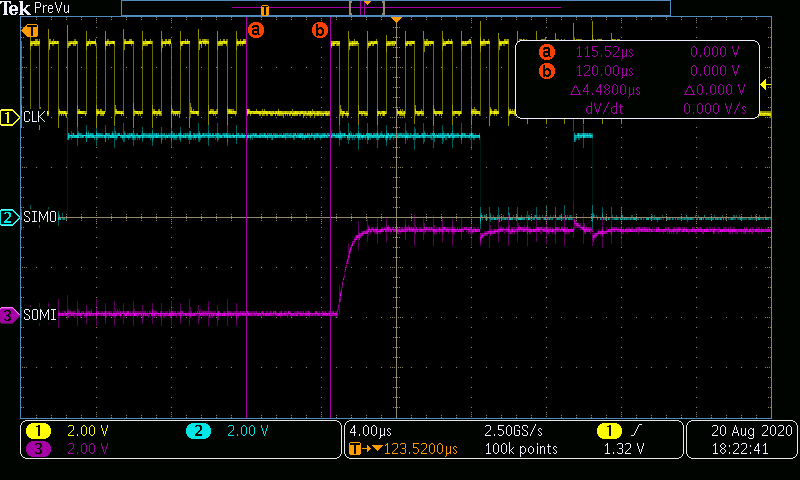

The other thing is that for this 20 microsecond delay I am only observing roughly 4.48 microseconds in CRO. Why this happens? But the SPI clock frequency 1 MHz is correctly observed.

Crystal frequency is 100 MHz and SPI clock frequency is 1 MHz which correct.

Thank you,

Vineeth N