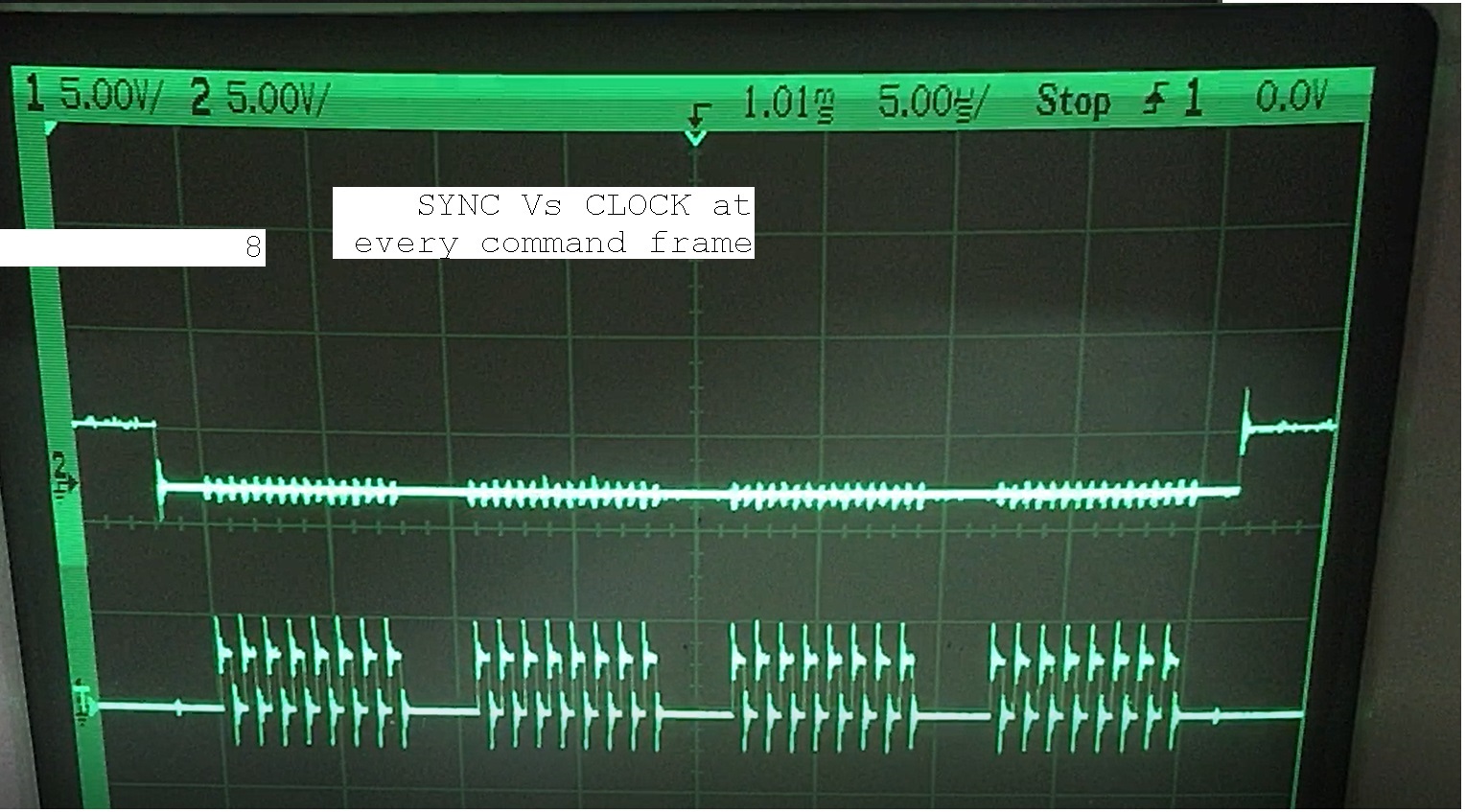

Hello, Regarding the SYNC (CHip Select) laws of Dac80004.

1.What is the Maximal amount bits I can send over MOSI for a single Low Sync(Chip select) session?

2.What is the minimal amount of time SYNC (Chip select) has to be high in order for the DAC to recognise that the SPI sesion is OVER?

3.If i Send my 32 bit command in 4 different 8bit Sync sessions,will the Dac recognise it as a valid command of 32bits?

Thanks.