Hi,

We have implemented a design with two Daisy-chained ADS1299 and are having some issues receiving data from the second IC.

We have correctly validated the 8 channel version, but when trying to talk to the daisy chained 16 channel version, the last 8 channels data is all 0. I have checked power, and all the signals, and everything seems to be fine except that DOUT from the second ADS1299 is always 0. It seems that something is pulling it to low all the time, and no matter in which state we are this signal is 0. I have checked impedance respect ground when not trying to communicate and is not shorted.

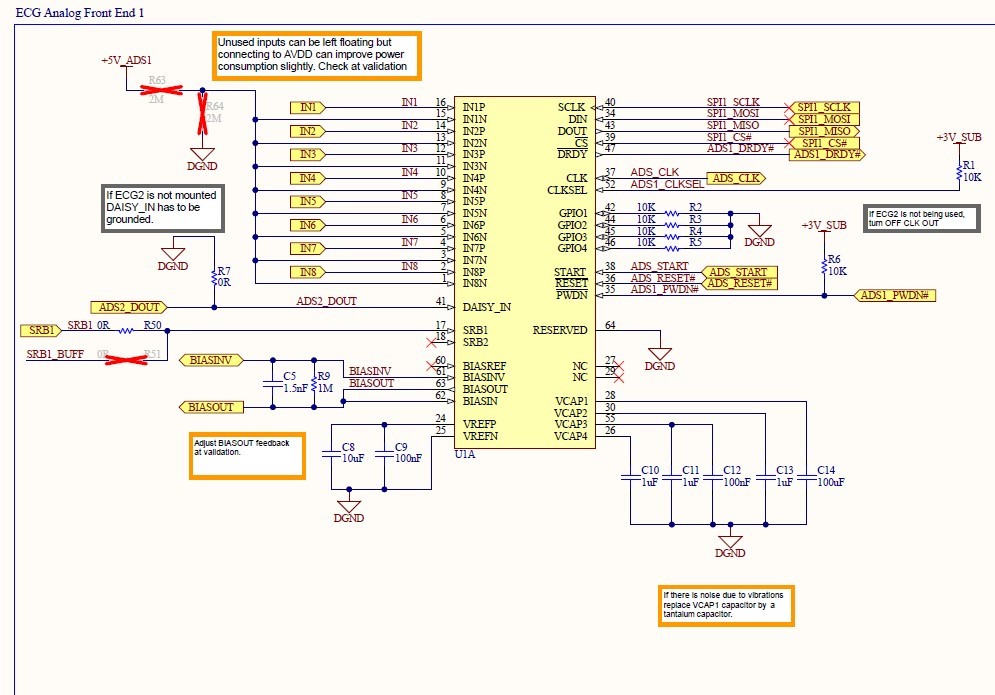

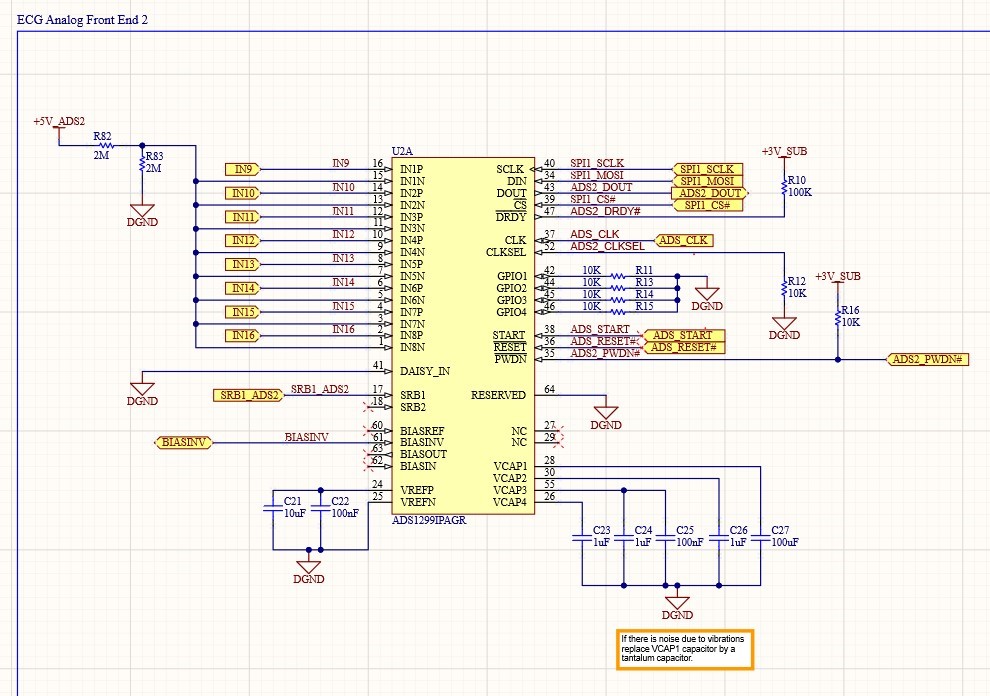

The schematics are the following, but we have removed R7 to enable the daisy chain and R82 and R83 are not assembled.

The register configuration is the following:

app: config1: 0xB4

app: config2: 0xC0

app: config3: 0xFC

app: config4: 0x0

app: ch1set: 0x60

app: ch1set: 0x60

app: ch2set: 0x60

app: ch3set: 0x60

app: ch5set: 0x60

app: ch6set: 0x60

app: ch7set: 0x60

app: ch8set: 0x60

app: loff: 0x3

app: loffsensp: 0x0

app: loffsensn: 0x0

app: biassensp: 0xFF

app: biassensn: 0xFF

app: misc1: 0x20

Any ideas on what might be the issue or how to keep troubleshooting? We are out of ideas.

Thank you for your help.

Best regards