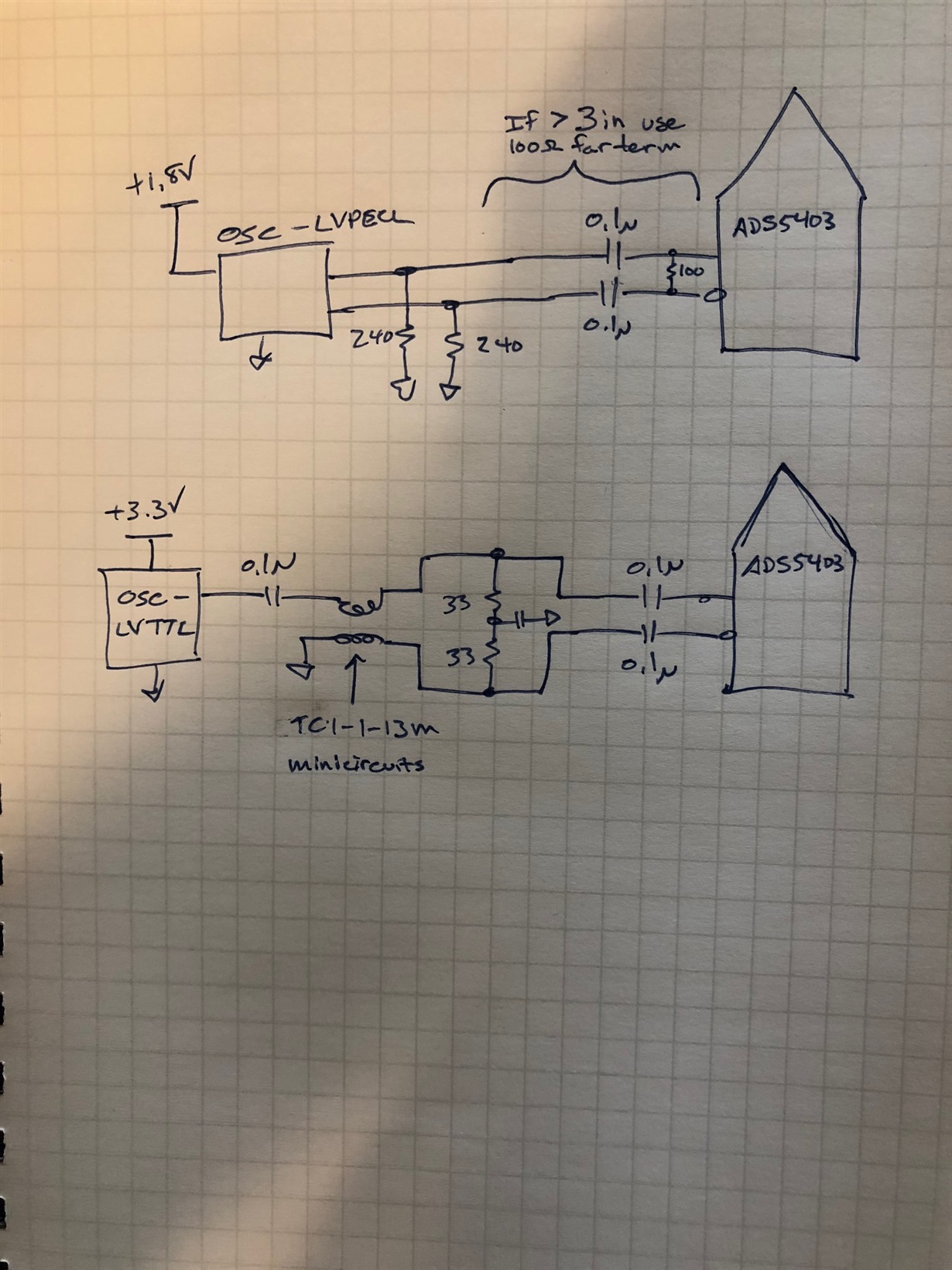

We designed an FPGA/ADC board using the 5403. 1/3 boards do not function and prior to a re-spin I want to make sure that I am using the LVPECL oscillator configuration correctly or should I use a capacitvely coupled LVDS oscillator. Please advise if possible.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.