Other Parts Discussed in Thread: LM3409

Hello,

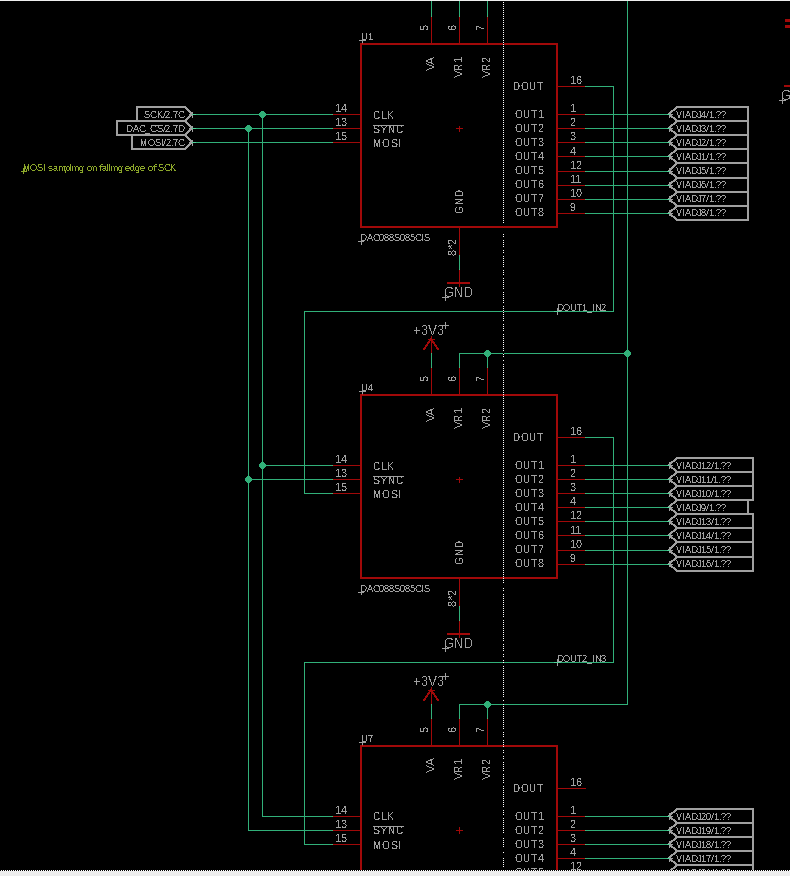

I try to make 3 DAC088S085 working in daisy chain mode.

I am able to make the first 2 IC working with good analog outputs but the third one does not work even in WRM or WTM.

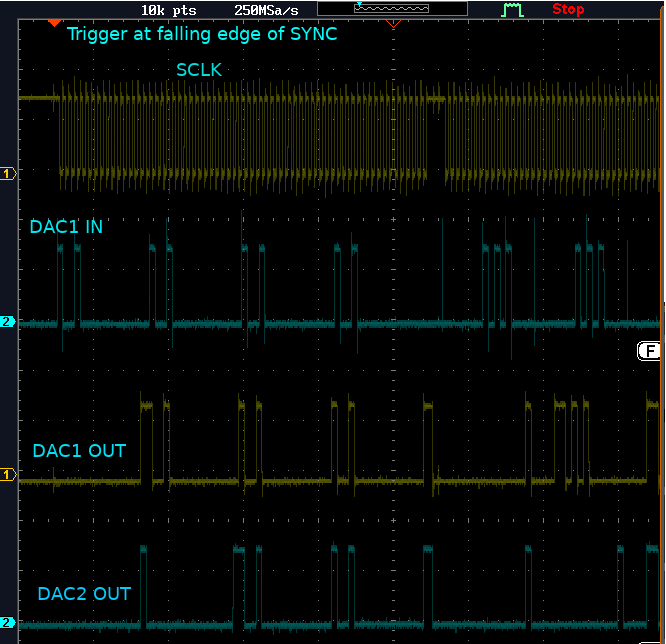

What I can see on scope is that at the first IC DIN and DOUT are out of phase for about 90°. Here is my mesurement :

Top channel is the input from MOSI, second is SCLK and third id the IC's DOUT. Is that normal?

So taht the first IC is sampling data on falling edges of SCLK but others (second and third) are sampling on rising edge.

I tried replacing all IC, checking soldering (these are WQFN packages). I tried removing IC #2 and #3 but same result.

Any idea ? Thanks.

Serge