Hi

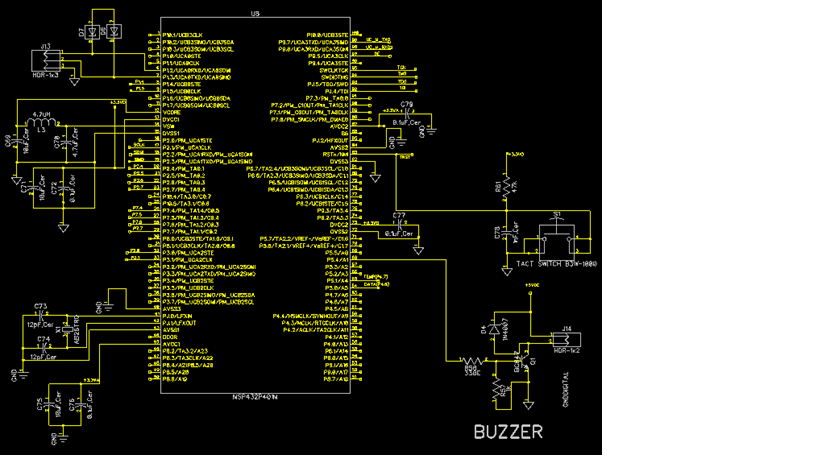

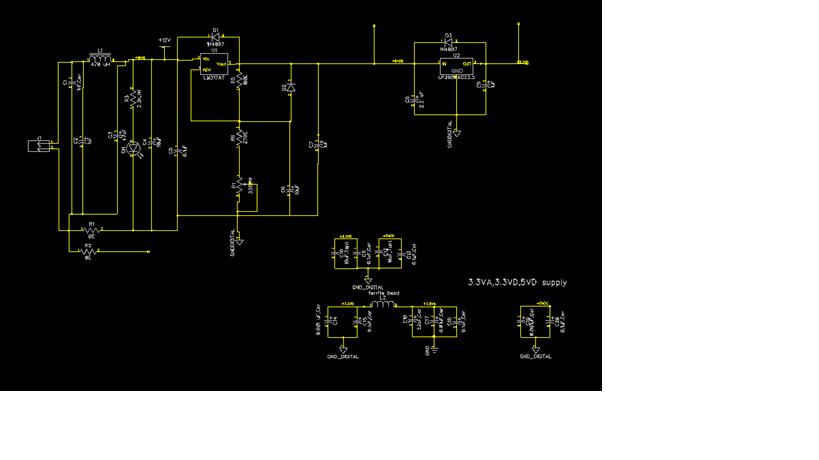

I am using ADS114S08 with MSP432 for interfacing PT100 probes. I have attached the code and ckt with this question.

I have attached the code and ckt with this question.

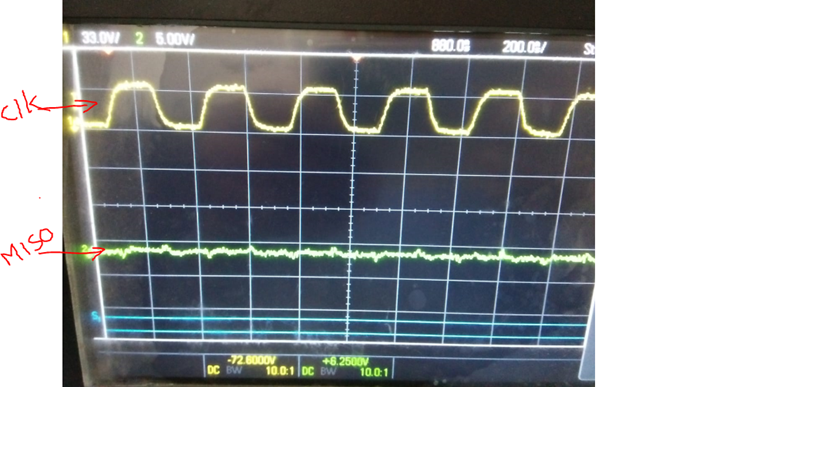

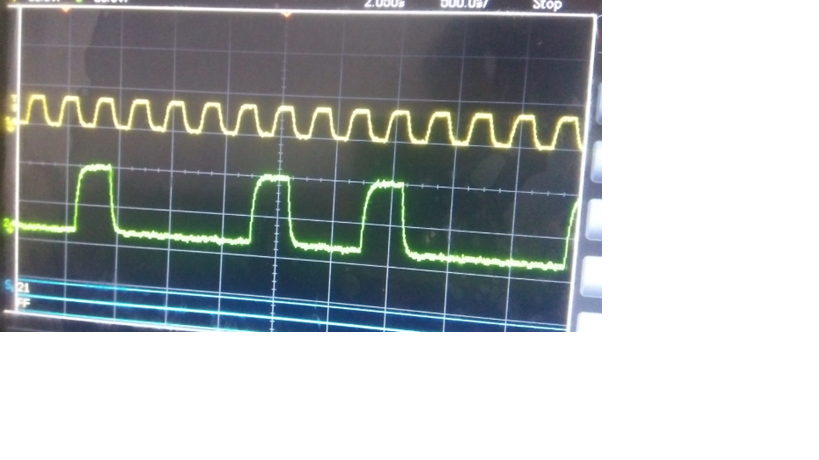

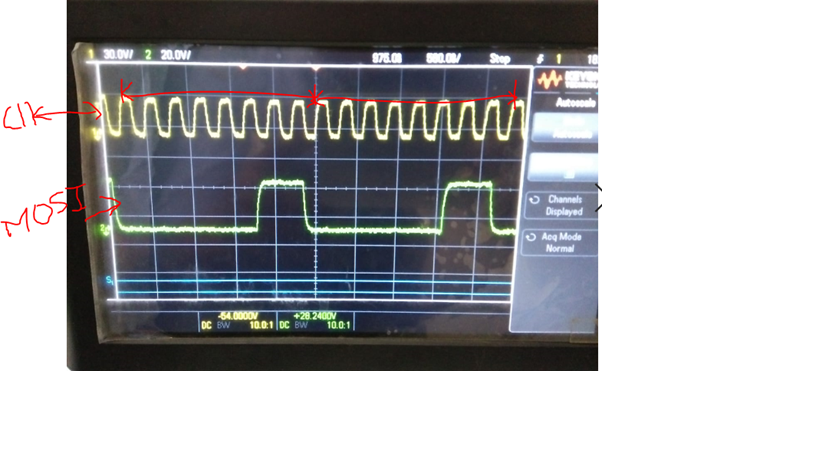

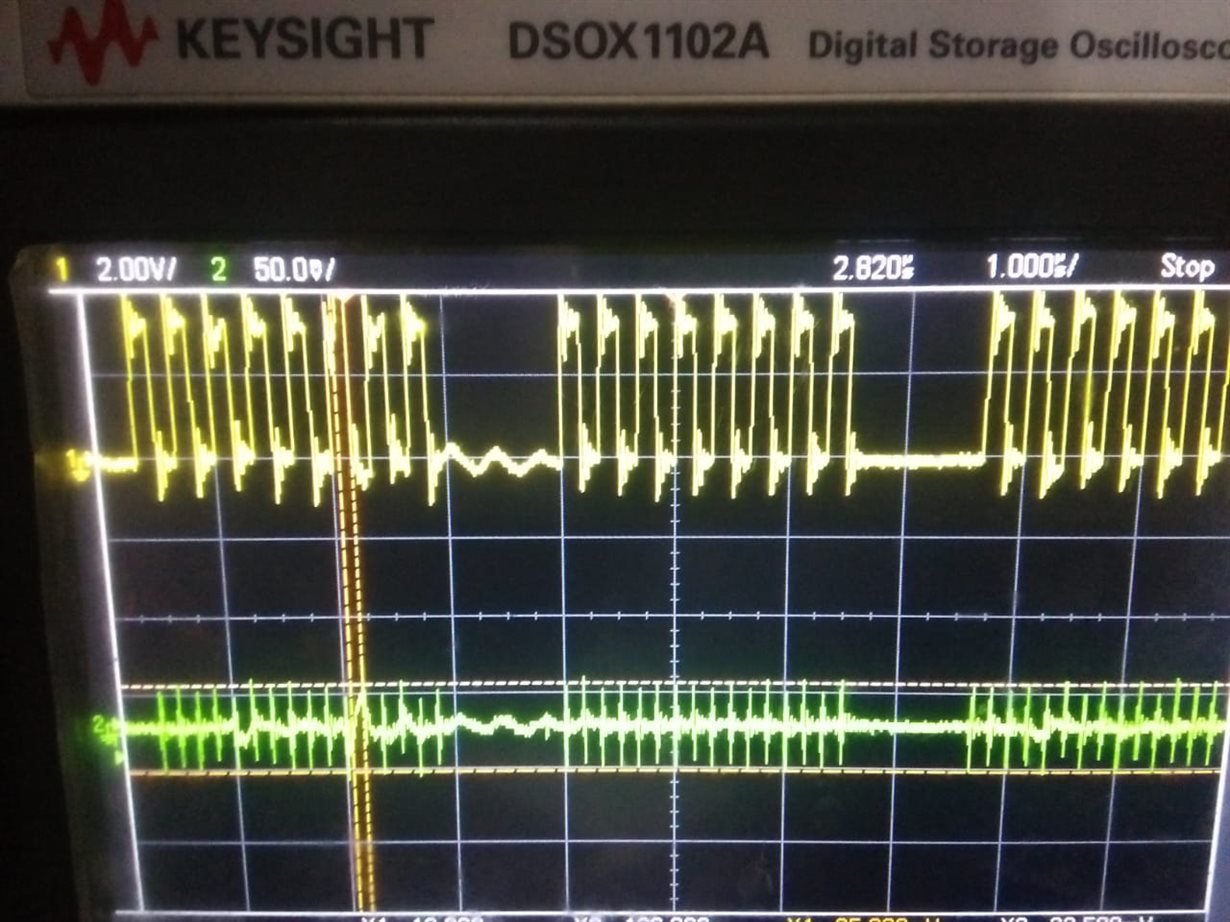

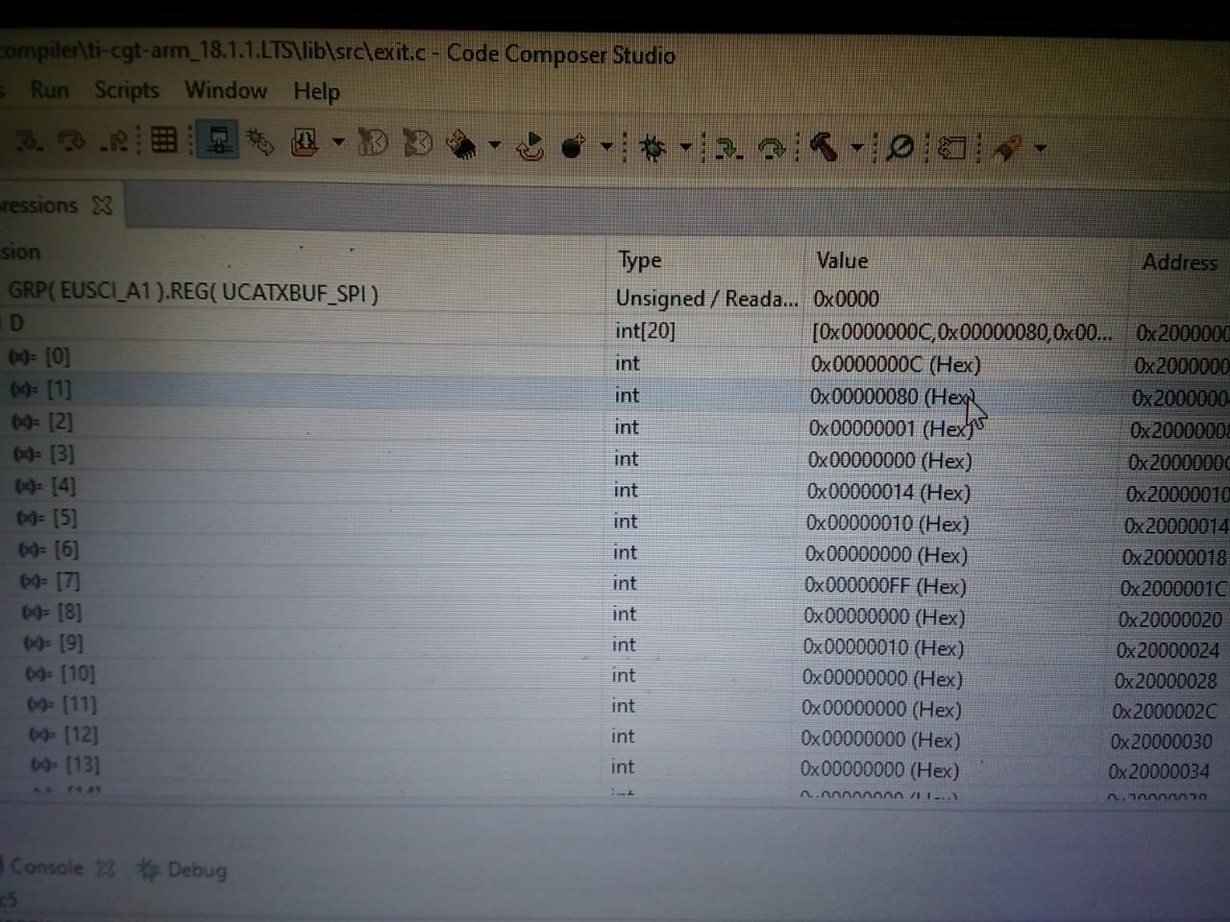

When the code is executed in a step by step manner the correct values are read about half the time but when the same code is executed in Run mode it gives 0x00 or 0xFF values.

#include "msp.h"

#include <ti/devices/msp432p4xx/driverlib/driverlib.h>

int i,D[16];

unsigned int D[16];

void dev_init_48M(void);

void SPI_INT();

void Read_Adc_reg();

void spi_tx(uint8_t txdata);

void spi_rx();

void Reset();

void Delay_Ms();

void main(void)

{

WDT_A->CTL = WDT_A_CTL_PW | WDT_A_CTL_HOLD; // stop watchdog timer

dev_init_48M(); //initialize device at 48MHz

P1->DIR &=~BIT5;

P1->REN |= BIT5; //set p1.5 as input

P1->OUT |= BIT5;

P2->DIR |= BIT4; // p2.4 as output cs pin to ADC

P1->DIR |= BIT4; // p1.4 as output reset pin to ADC

P1->OUT |= BIT4; // tie p1.4 to high

SPI_INT(); //spi setup

Read_Adc_reg();

}

void dev_init_48M(void)

{

/* Step 1: Transition to VCORE Level 1: AM0_LDO --> AM1_LDO */

while ((PCM->CTL1 & PCM_CTL1_PMR_BUSY));

PCM->CTL0 = PCM_CTL0_KEY_VAL | PCM_CTL0_AMR_1;

while ((PCM->CTL1 & PCM_CTL1_PMR_BUSY));

/* Step 2: Configure Flash wait-state to 1 for both banks 0 & 1 */

FLCTL->BANK0_RDCTL = (FLCTL->BANK0_RDCTL & ~(FLCTL_BANK0_RDCTL_WAIT_MASK)) |

FLCTL_BANK0_RDCTL_WAIT_1;

FLCTL->BANK1_RDCTL = (FLCTL->BANK0_RDCTL & ~(FLCTL_BANK1_RDCTL_WAIT_MASK)) |

FLCTL_BANK1_RDCTL_WAIT_1;

/* Step 3: Configure DCO to 48MHz, ensure MCLK uses DCO as source*/

CS->KEY = CS_KEY_VAL ; // Unlock CS module for register access

CS->CTL0 = 0; // Reset tuning parameters

CS->CTL0 = CS_CTL0_DCORSEL_5; // Set DCO to 48MHz

// Select MCLK = DCO=48MHz and Configure SMCLK=MCLK/16= 3MHz(SMCLK source divider)

CS->CTL1 = CS->CTL1 & ~(CS_CTL1_SELM_MASK | CS_CTL1_DIVM_MASK) | CS_CTL1_SELM_3 | CS_CTL1_SELS_3 | CS_CTL1_DIVS_4;

CS->KEY = 0; // Lock CS module from unintended accesses

// Enable global interrupt

__enable_irq();

}

void SPI_INT()

{

P2->SEL0 |= BIT1 | BIT2 | BIT3; // set 4-SPI pin as second function

//Configure microcontroller for SPI mode 1 (CPOL = 0, CPHA = 1)

EUSCI_A1->CTLW0 |= EUSCI_A_CTLW0_SWRST; // Put eUSCI state machine in reset

EUSCI_A1->CTLW0 = EUSCI_A_CTLW0_SWRST | // Remain eUSCI state machine in reset

EUSCI_A_CTLW0_MST | // Set as SPI master

EUSCI_A_CTLW0_CKPH | // Clock phase select

EUSCI_A_CTLW0_SYNC | // Set as synchronous mode

EUSCI_A_CTLW0_MSB| // MSB first

EUSCI_A_CTLW0_MODE_0 | // 3-pin mode

EUSCI_A_CTLW0_SSEL__SMCLK; // SMCLK

EUSCI_A1->BRW = 0x01; // /2,fBitCl0ock = fBRCLK/(UCBRx+1).

EUSCI_A1->CTLW0 &= ~EUSCI_A_CTLW0_SWRST; // Initialize USCI state machine

}

void Read_Adc_reg()

{

Reset();

spi_rx();

}

void Reset()

{

Delay_Ms();

spi_tx(0x06);

Delay_Ms();

Delay_Ms();

}

void spi_tx(uint8_t txdata)

{

P2->OUT &=~BIT4; // CS at low

Delay_Ms();

while(!(EUSCI_A1->IFG & EUSCI_A_IFG_TXIFG));

EUSCI_A1->TXBUF = txdata ;

while( UCA1STATW & UCBUSY);

P2->OUT |=BIT4; // CS at high

}

void spi_txnop(uint8_t txdata)

{

while(!(EUSCI_A1->IFG & EUSCI_A_IFG_TXIFG));

EUSCI_A1->TXBUF = txdata ;

while( UCA1STATW & UCBUSY);

}

void spi_rx()

{

spi_tx(0x22); // RREG starting at 01h address(1st byte) status reg.

spi_tx(0x10); // 1 res. To read (2nd byte)

P2->OUT &=~BIT4; // CS at low

for(i=0;i<16;i++)

{

spi_txnop(0x00); //1 nop command to read one reg

while (!(EUSCI_A1->IFG & EUSCI_A_IFG_RXIFG));

D[i] = EUSCI_A1->RXBUF; // Move data to a temporary buffer D

Delay_Ms();

}

P2->OUT |=BIT4; // CS at low

}

void Delay_Ms()

{

int k,j;

for(k=0;k<100;k++)

{

for(j=0;j<2000;j++);

}

}