Hi,

I hope that someone can help me with this issue we recently discovered.

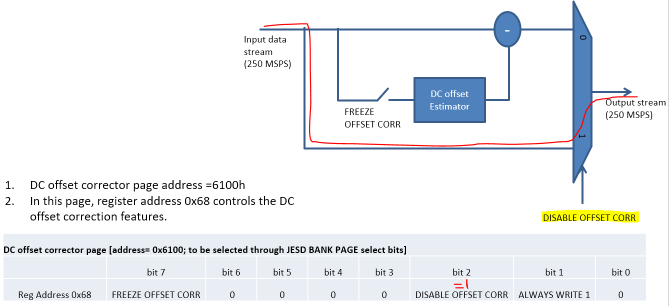

We're using ADS54J40 in a DC-coupled design. We use only channel A, everything of channel B that we could disable is disabled. We have disabled VCM compensation (master page reg 0x4F = 0x01) and completely bypassed the interleaving offset correction (reg 0x6068 = 0x06)

In most of our modules this works very well (~75%, not a lot of statistics yet). Stable DC inputs give stable raw ADC outputs, with just a few LSB of noise.

However, in some modules we see weird offset jumps. It's a very regular pattern, the same pattern for at least 2 different modules: every 1.6seconds there's a 40ms period where the ADC output jumps.

Even weirder is that this only seems to occur when the ADC diff input voltage is in the range of ~+0.53V to +0.89V. Outside this voltage range we don’t observe the jumps.

Table below shows the 4 sub-ADC channel outputs for a clean DC +0.756V differential input at the ADC.

Sub-ADC #2 doesn’t show any jump, #1 and #3 show a +61LSB jump, and #4 shows a +100LSB jump:

|

NORMAL |

JUMP |

diff |

||

|

ADC raw LSB |

subADC1 |

6602 |

6665 |

62 |

|

subADC2 |

6525 |

6525 |

1 |

|

|

subADC3 |

6446 |

6508 |

61 |

|

|

subADC4 |

6524 |

6624 |

101 |

|

|

average |

6524 |

6580 |

56 |

We have ruled out a lot of external factors that could cause this jump, and now we’ve come so far that we think it’s an artefact caused by something inside the ADC.

Did someone observe this behavior before? Is there a solution for this? It’s really affecting the performance of our module.

Best regards,

Paul