Hi,

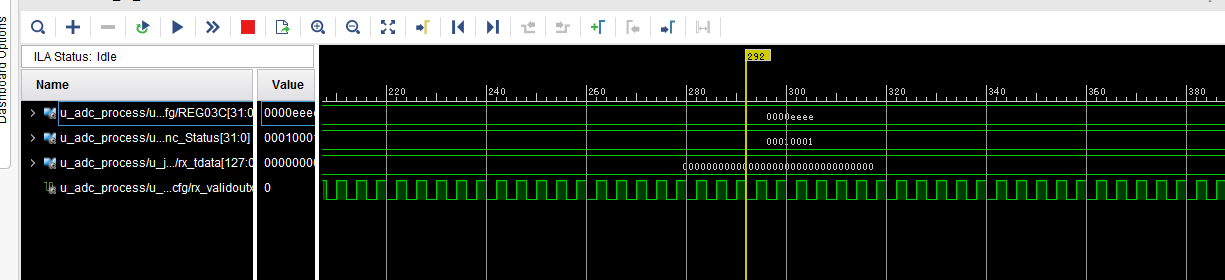

ADS54J60 connected with FMC and K7,now the JESD204B has no problem, the PHY data is high and the JESD204B status appears that the data is detected. He used the 4244 mode, each channel appears eeee.

Link Debug status Lane 0

Bit 3: 1 = Start of Data was Detected

Bit 2: 1 = Start of ILA was Detected

Bit 1: 1 = Lane has Code Group Sync

Bit 0: 1 = Lane is currently receiving K28.5's (BC alignment characters)

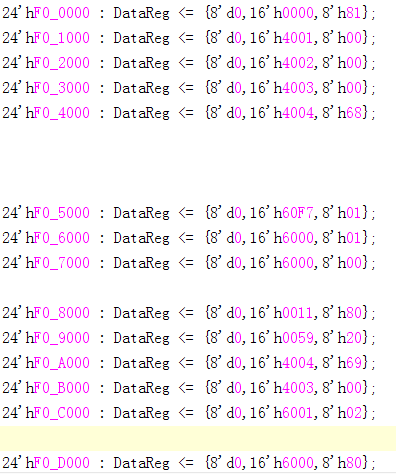

ads54j60 data Sequence :

Best regards

Kailyn