Other Parts Discussed in Thread: LMK04828, TSW14DL3200EVM,

Hi,

I have some questions about the reference design you provided previously.

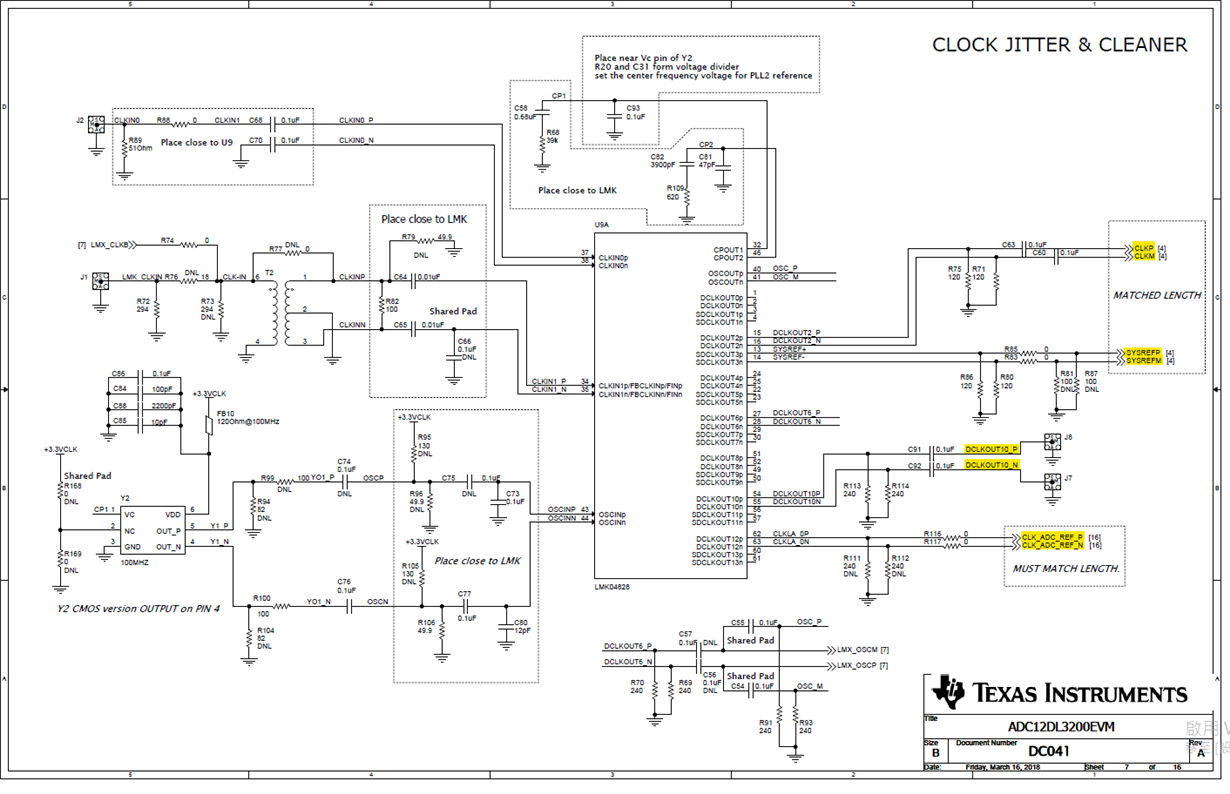

The image below is LMK04828 from the schematic file. When operating in external clock mode, I found that none of the outputs from LMK04828 was actually used. CLKP/M were not used. The SYSREF calibration described in the 7.3.4.3.1 ~ 7.3.4.3.2 wasn't executed, thus no signal coming out from SYSREFP/M. DCLKOUT10_P/N and CLK_ADC_REF_P/N were not used in the reference design either. Is LMK04828 not necessary in this circumstance?

Best Regards,

Alec