Hello,

I am attempting to get a reading from the ADS124S08. The device is being initialized in singled ended mode using ANCOM (pin 1) as the negative input selection (ANCOM is grounded). I am using a raspberry pi 4 and the SPIDEV library in order to send commands to the chip.

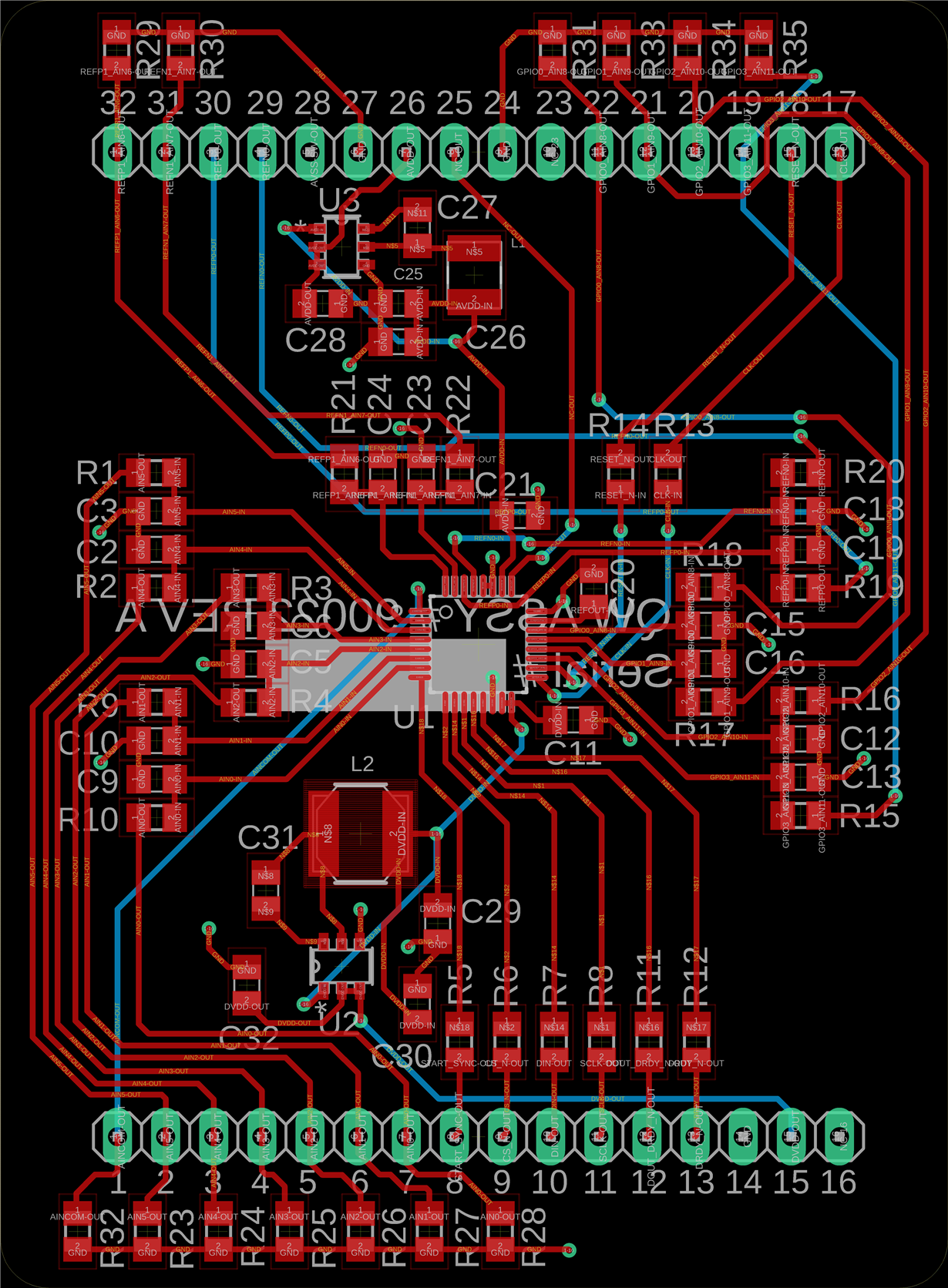

I have attached my python code along with a board layout designed in EAGLE. I have communicated with the chip only through commands and reading the registers. I plan to use AIN0-AIN11 but for testing purposes I am trying to get AIN0 working for now.

-----Declared Registers----

Input Multiplexer Register (0x0C)

Gain Setting Register (0xE0)

Data Rate Register (0x74)

REF (0x19)

IDACMAG (0X00)

IDACMUX (0XFF)

VBIAS (0X00)

SYS (0X11)

OFCAL0 (0X00)

OFCAL1 (0X00)

OFCAL2 (0X00)

FSCAL0 (0X00)

FSCAL1 (0X00)

FSCAL2 (0X40)

GPIODAT (0X00)

GPIOCON (0X00)

import spidev

from time import sleep

import os

import sys

#clear terminal

os.system("clear")

sys.tracebacklimit = 0 #suppress traceback errors

#----------Initialize Variables/Commands----------#

SPI_BUS = 0 # spidev0

SPI_DEVICE = 0 # spidev0.0

SPI_CLOCK = 125000 # 125 kHz limit

# setup SPI

spi = spidev.SpiDev()

spi.open(SPI_BUS, SPI_DEVICE)

spi.max_speed_hz = SPI_CLOCK

spi.mode = 1

NOP = 0x00 #no operation command

WAKEUP = 0x02 #wakeup command

PWRDWN = 0x05 #powerown command

RESET = 0x06 #reset command

START = 0x08 #start command

STOP = 0x0A #stop command

RDATA = 0x13 #read data command

#function to handle the SPI communication and print the command to terminal

def output(varName, cmd):

print(varName)

print(" Sent to ADC --------->", cmd)

data_in = []

data_in = spi.xfer(cmd, 100000)

print(f' Received from ADC ---> {data_in}')

print("------------------------------------------------------")

sleep(0.3)

try:

#----------Initialize ADC send----------#

output("WAKEUP - 0x02", [NOP, WAKEUP]) #wakeup ADC

output("RESET- 0x06", [NOP, RESET]) #reset ADC

output("Declare PGA, Data Rate, Reference, Exciation Registers",[0x43, 0x02, 0xE0, 0x74, 0x19]) # Start at 3rd register and declare registers 3,4,5

output("Declare System Control Register",[0x49, 0x00, 0x11]) # declare register 9

output("Input Multiplexer to 0x1C",[0x42, 0x00, 0x0C])

output("START - 0x08", [START]) #start ADC

n = 0

while True:

output(f"[{n}] Status",[0x21,0x00,0x00])

output(f"[{n}] RDATA COMMAND",[0x12,0x00,0x00,0x00,0x00])

n = n + 1

sleep(3)

finally:

print("Stopping...\n")

output("STOP", [STOP])

output("PWRDWN", [PWRDWN,NOP,NOP])

spi.close()

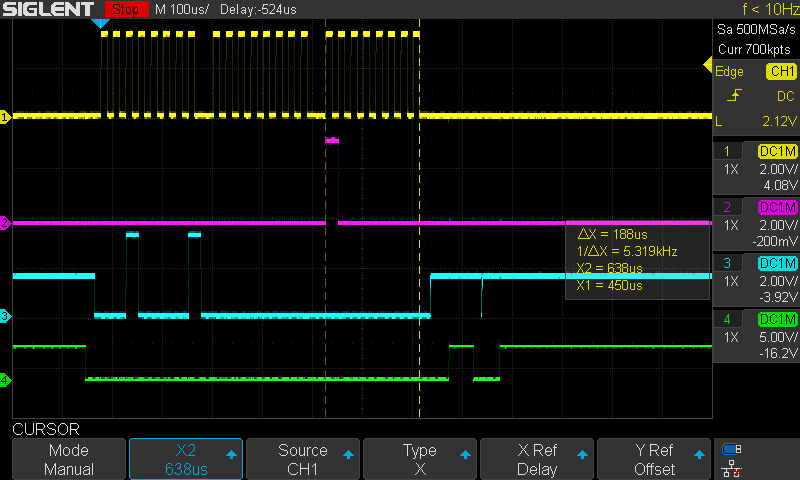

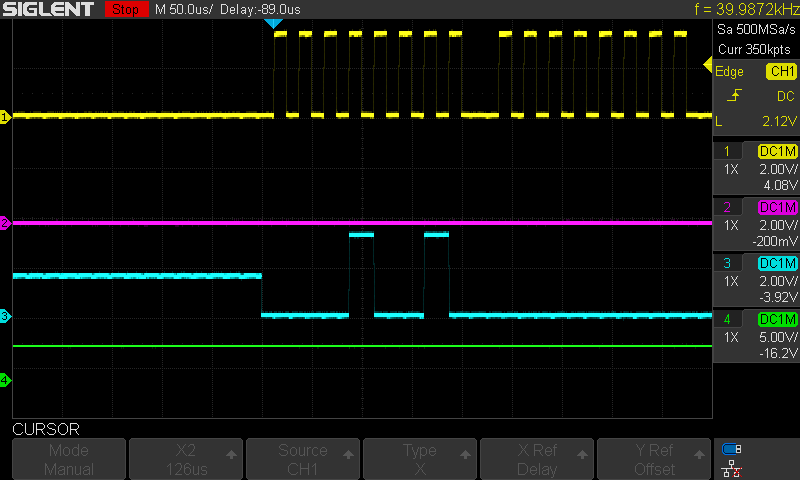

Read status bit 0x21 (decimal 33) sent to adc. 0x80 (decimal 128 or binary 0b10000000) returned. This is due to not clearing the FL_POR flag in the status register for testing. The SENDSTAT bit in register has been turned on. When the RDATA command is sent I should be receiving 128 followed by 3 bytes of information. I have only received zeros back every time the RDATA command is issued.

Any help would be appreciated. If more information is needed please let me know.