Other Parts Discussed in Thread: CDCLVP1102, , LMH2832, LMZ12003

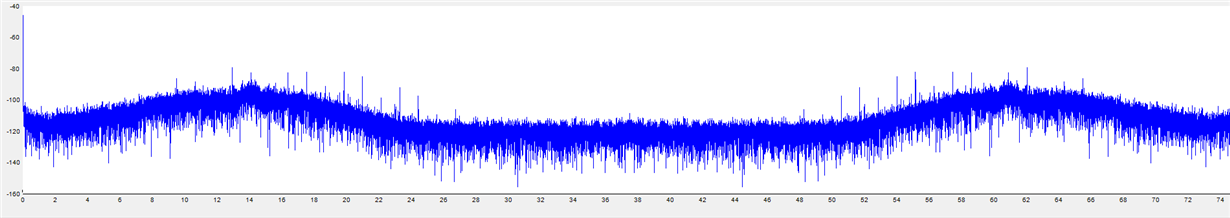

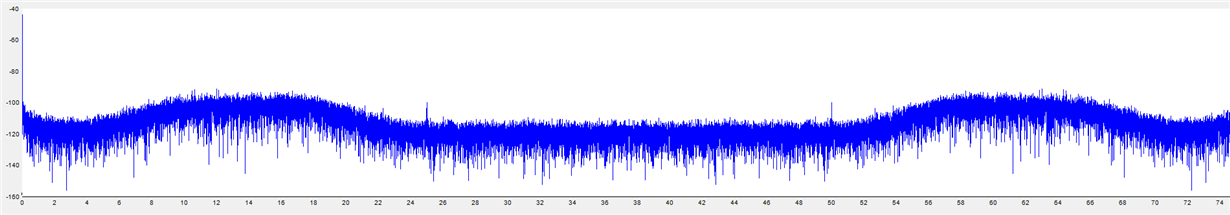

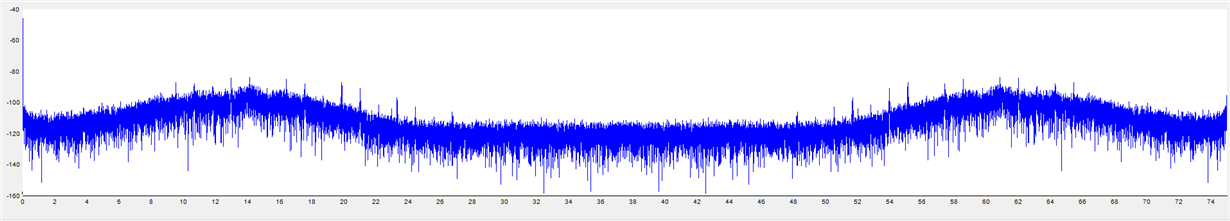

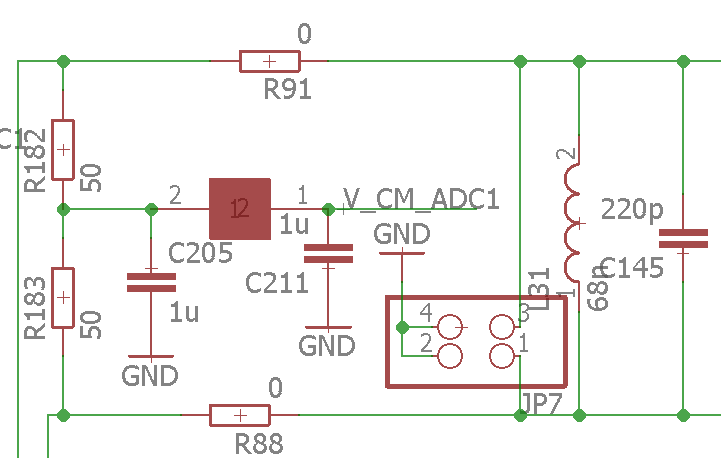

What is the register mapping for the LVDS swing? The data sheet doesn't provide any information. I have some spurs due to the digital signals and I have tried simply all 256 values. I have found a setting, where the spurs are reduced, but now the data transfer has sometimes errors. I need a description for an advanced optimization.