Hi,

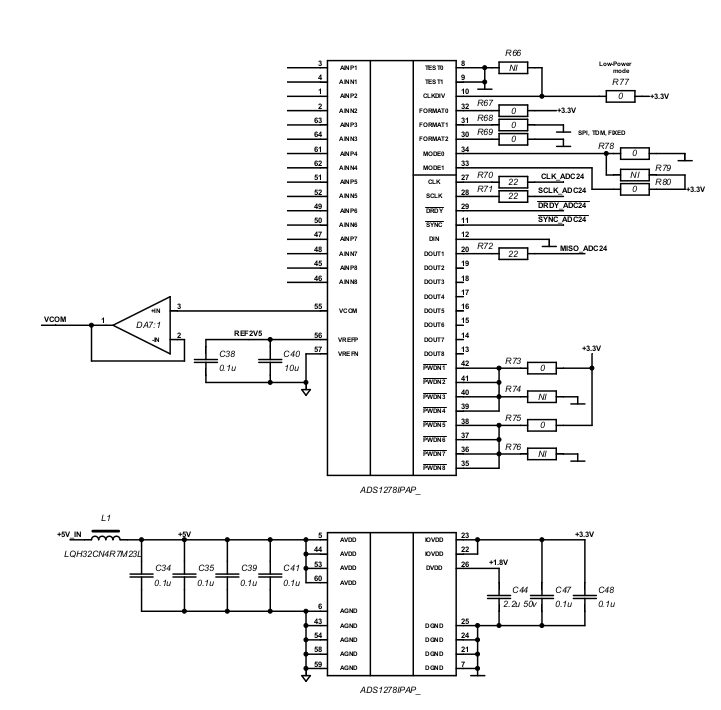

I am working with ADS1278.

Configuration is

Low power mode, SPI, TDM, FIXED

CLK = 25 MHz

SCLK = 25 MHz

DRDY = 48 kHz

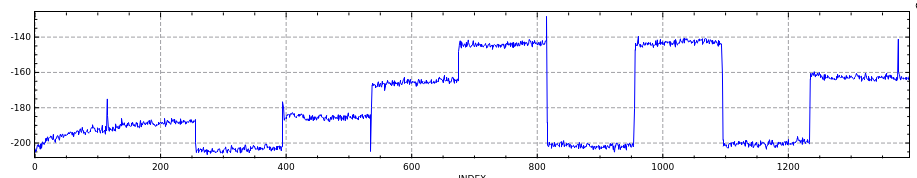

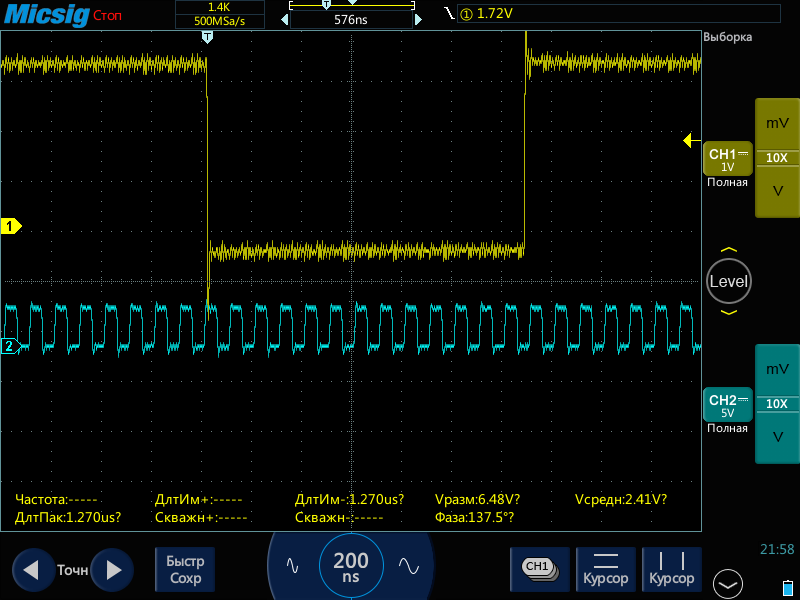

The problem is in random offset (+-100 lsb) at power on and / or CLK restart.

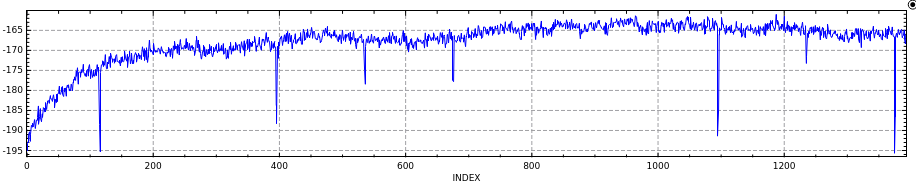

After some experiment I've found that

1. Offset appears after stop / start timer in microcontroller which used to generate CLK

2. Offset doesn't apper after enable / disable gpio on CLK pin while timer running

Is it normal behavior?