We have a design where around 1 of 8000 I2C transactions towards ADS7828 results in SDA line gets stuck low.

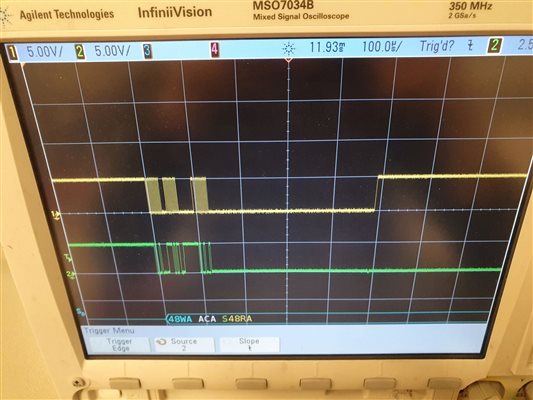

I managed to capture a transaction where this occurs.

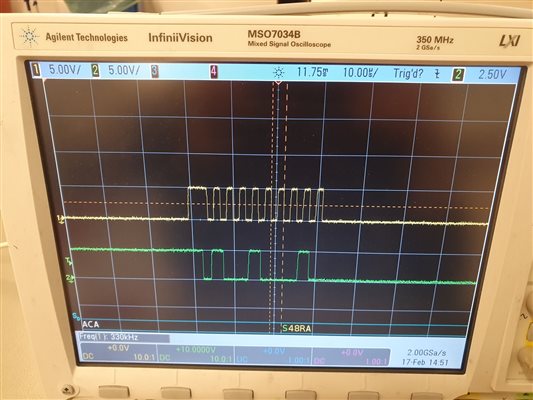

After a repeated start, it never releases the SDA line after address ACK.

What can cause this?

Transaction:

Close up:

Measured timings from the frame in question:

f_scl = 330 kHz

t_buf = 100 ms

t_hd,sta = 1.40 us (start)

t_hd,sta = 1.45 us (repeated start)

t_low = 1.46 us

t_high = 1.38 us

t_su,sta = 3.0 us

t_su,dat = 740 ns

t_hd,dat = 340 ns

t_rcl = 120 ns

t_fcl = 260 ns

t_rda = 120 ns

t_fda = 260 ns

t_su,sto = inf