Other Parts Discussed in Thread: , ADS7946, INA210, INA229, INA240

Hello TI experts,

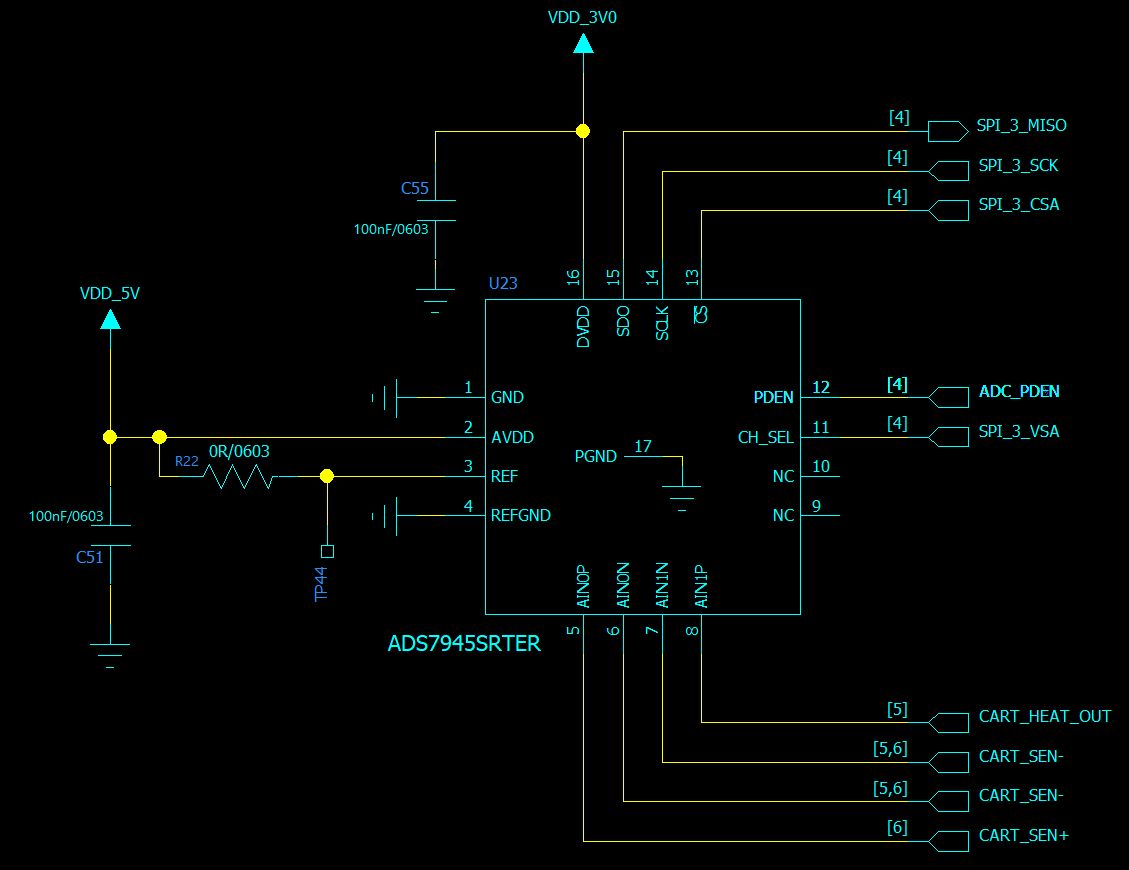

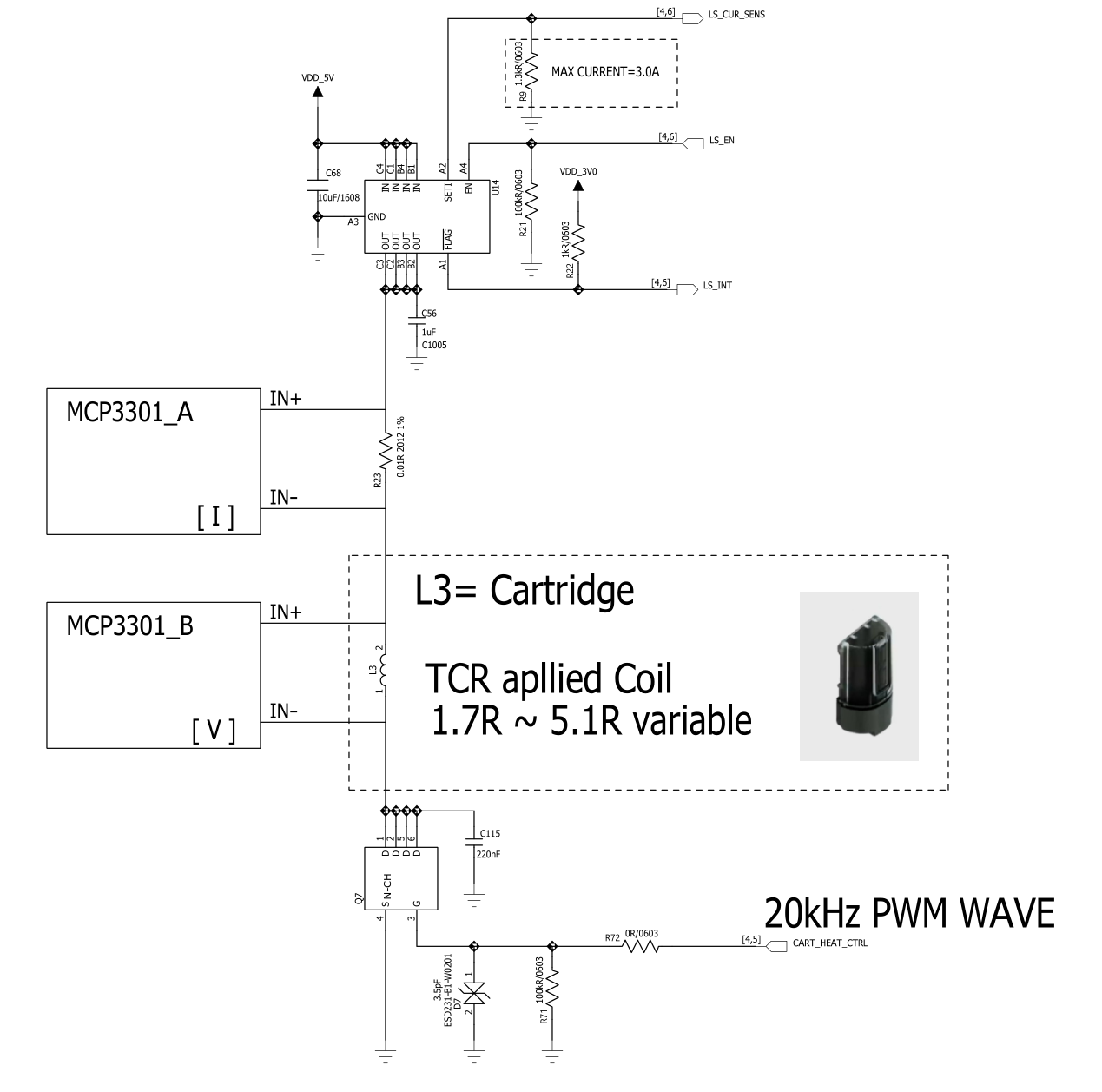

my customer considers ADS7945 for their product, they drew first schematic.

please review the schematic below;

they want to use 0V~5V PWM signal as input, and 3.0V for output digital signal.

so please check the voltage of AVDD, REF, DVDD are right.

and i have one more question, about power down mode in page 30 of datasheet.

in datasheet, "Note that the device looks at the PDEN status only at the CS rising edge"

then what is the first sequence? PDEN to 1 and make rising edge for \CS next? or first make rising edge for \CS and PDEN to 1 next??

how about from power down to normal operation? should we follow PDEN to 0 and \CS falling edge?

please give me a detailed description about this. Thank you.

Best regards,

Chase