Other Parts Discussed in Thread: LMK04828,

Hello,

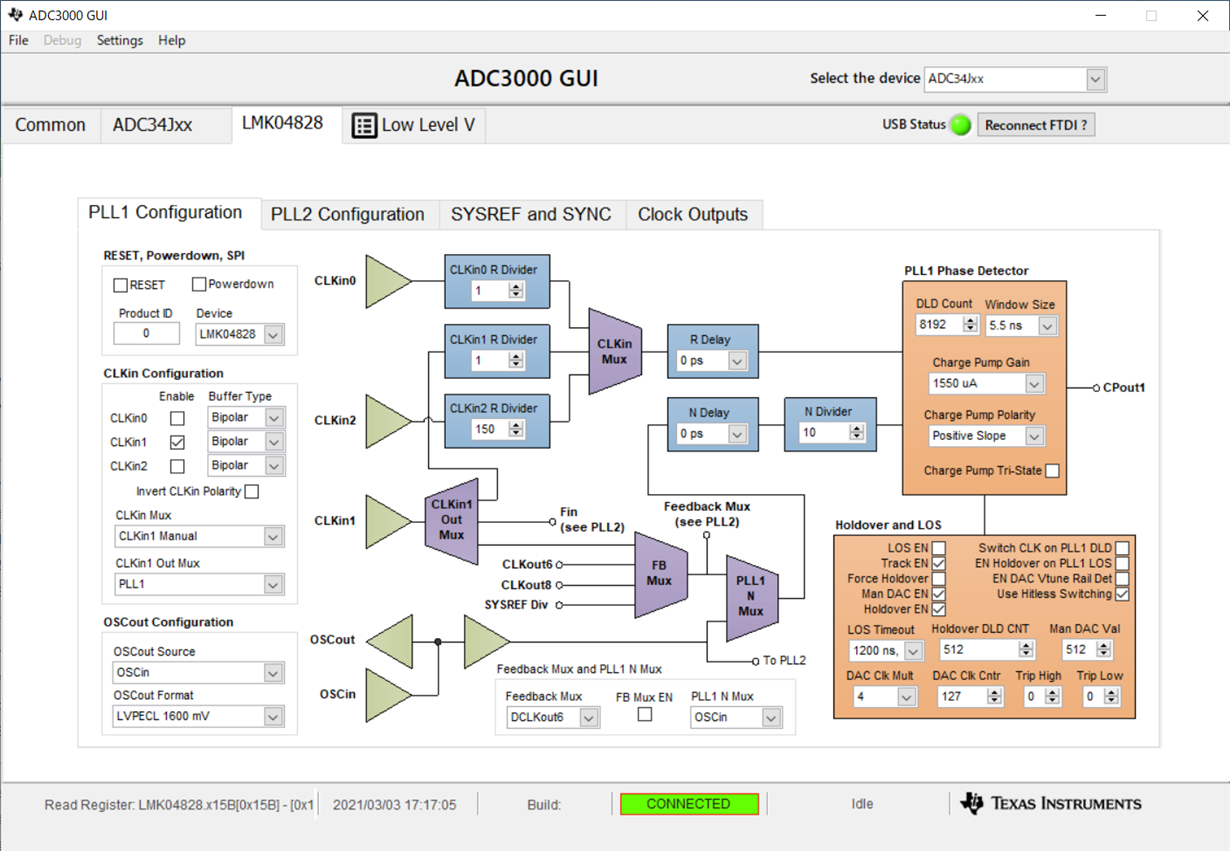

We have a problem that PLL1 of LMK04828 mounted on ADC34J45EVM does not lock by external clock (CLK1IN).

The external clock is a 10MHz sine wave.

LED D3(LMK LOCKED) is not turning on.

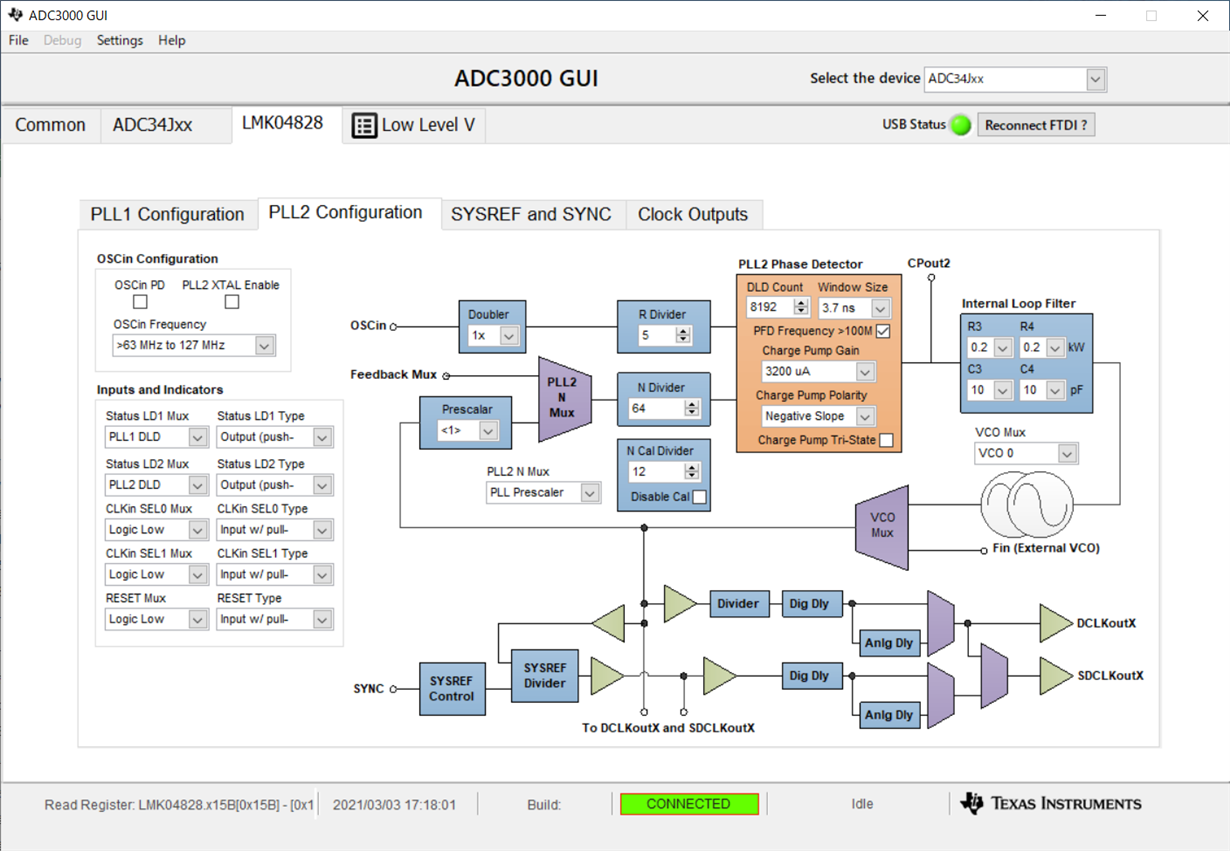

But, LED D4(PLL2 LOCKED) is turning on.

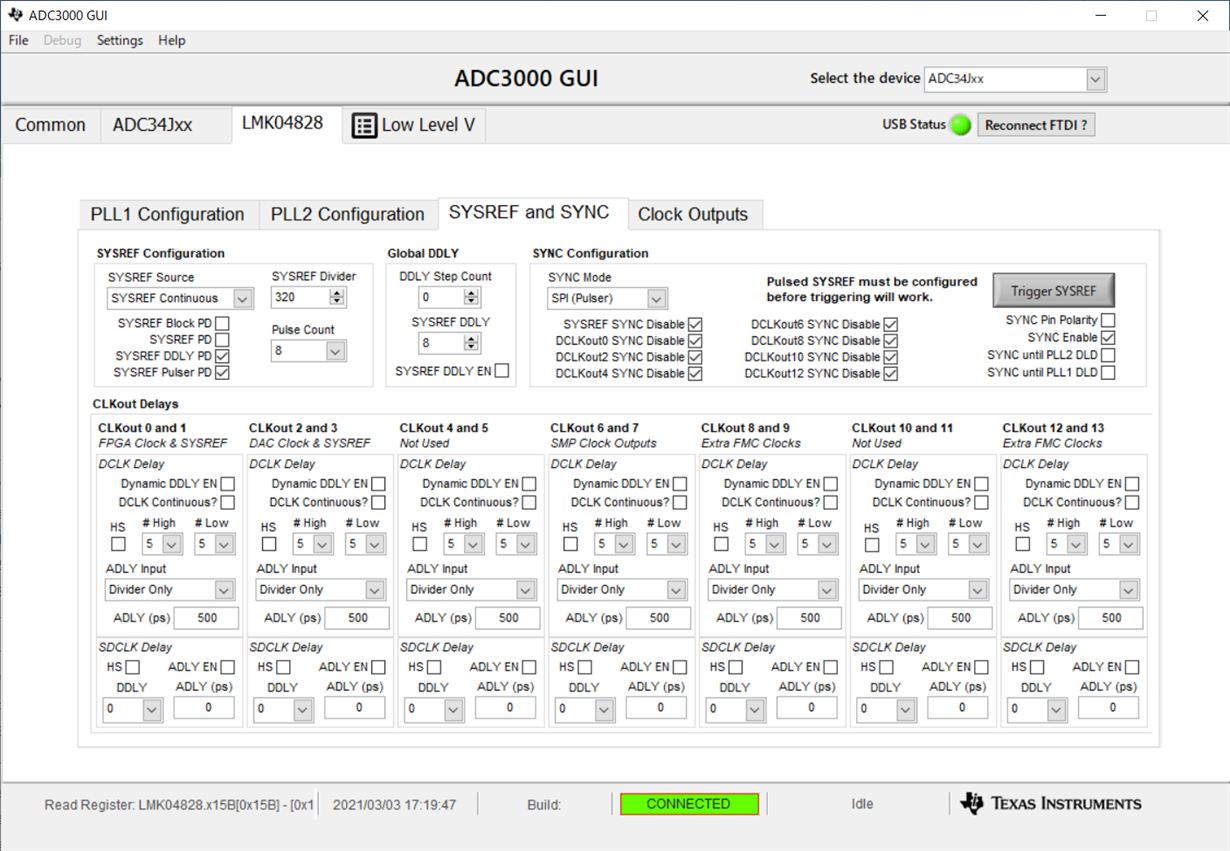

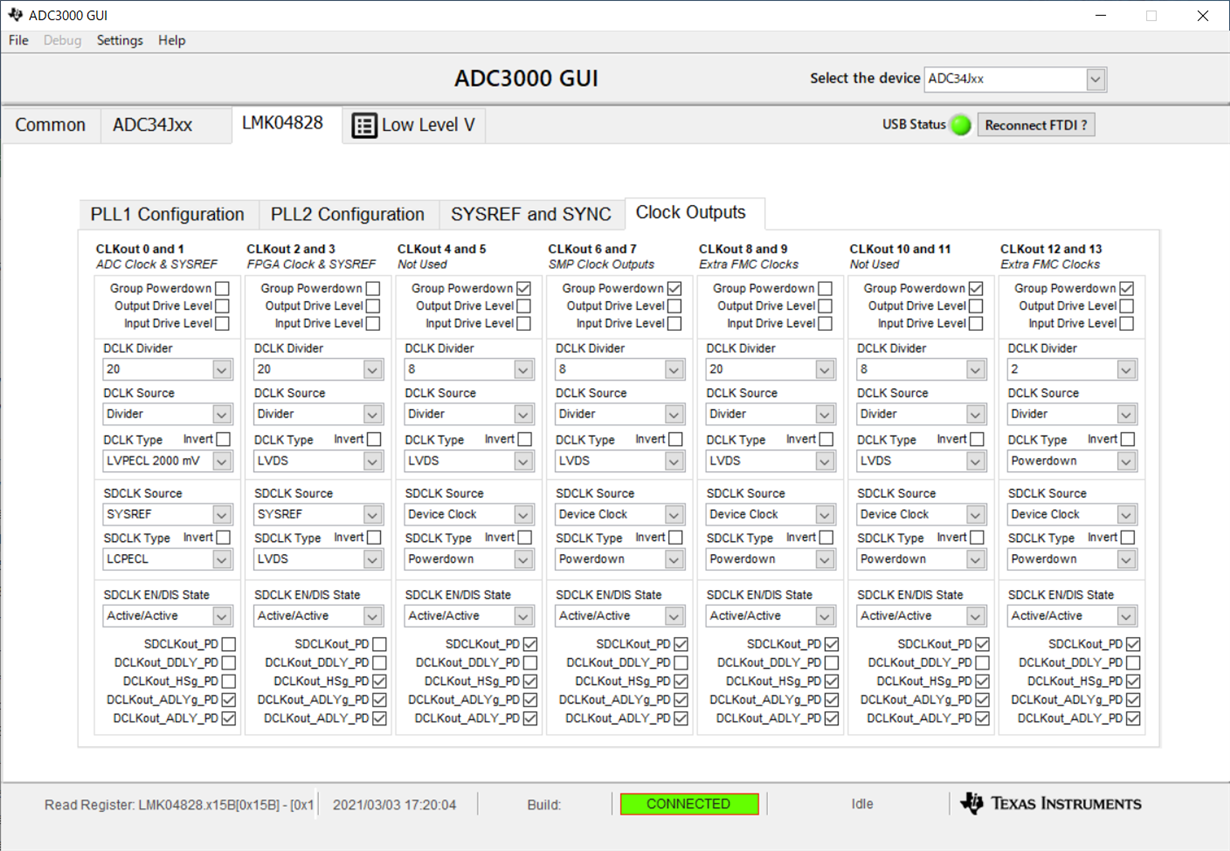

I've attached our ADC3000 GUI settings so can you tell me if there's anything wrong?

Regards.