Other Parts Discussed in Thread: ADS1248

Hi, I still have a problem with my ADC. Spikes are on every configuration of Measuring Bridge, parallel and series.

configuration:

static uint8_t m_tx_buf_CONF_1[] = {(WREG|INPMUX), 0x03, (MUX_P_AIN1|MUX_N_AIN0), (DELAY_64|PGA_ON|GAIN_128), (G_CHOP_ON|CLK_INT|MODE_SS|FILTER_LL|SPS_2000), (REFP_BUF_EN|REFN_BUF_EN|REF_0|INT_REF_ON_WHEN_CONV)};

static uint8_t m_tx_buf_CONF_2[] = {(WREG|INPMUX), 0x03, (MUX_P_AIN3|MUX_N_AIN2), (DELAY_64|PGA_ON|GAIN_128), (G_CHOP_ON|CLK_INT|MODE_SS|FILTER_LL|SPS_2000), (REFP_BUF_EN|REFN_BUF_DIS|REF_0|INT_REF_ON_WHEN_CONV)};

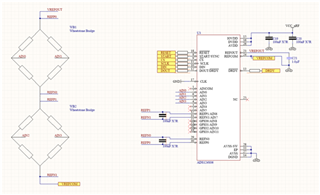

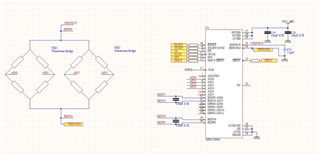

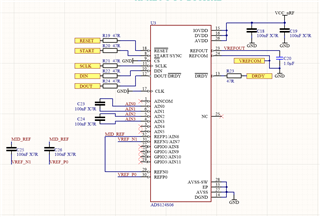

My design:

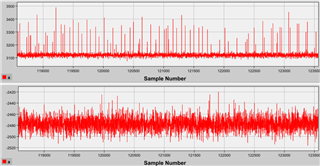

And also the data from converter: