Other Parts Discussed in Thread: ADS7863

Hello Team,

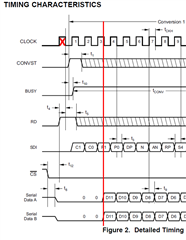

My customer is aware of the fact, that the ads7863a replaces the older version and they use the updated version in their design. Unfortunately they can't get sufficient timing information from the datasheet of the ads7863a.They can't seem to find any information on what edge the adc starts reading from sdi, or sends the first bit on sdoa/b.

Thanks in advance.

Regards,

Renan