Part Number: ADC128D818

Other Parts Discussed in Thread: ADS7128, OPA320

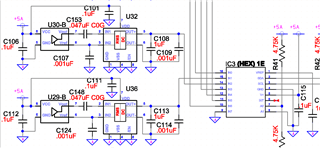

We are using ADC128D818 in continuous Mode with the internal 2.56V Reference, with the ADC powered from 5V.

In our example circuit, we are reading single ended values which are output from an LTC1966 RMS to DC converter, which has an output impedance of approximately 30k and whos output is buffered by a 1uF ceramic cap, and a 1nF Ceramic filter cap at the pins of ADC128D818.

Our expected analog voltage ranges from this circuit are between 100mV and 1.00V.

When we read back the raw ADC counts, we are consistently low by about 8 counts over the entire 100mV to 1.00V input range.

At first we expected that the ADC may be slightly loading the 30kohm Impecance of the RMS to DC converter, however, measurement with a 6digit DMM confirms that voltages at the ADC are as expected while the reported value is low by approximately 8 counts.

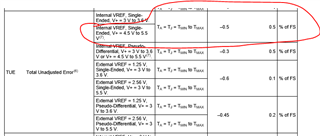

The 8bit offset is within the Total Unadjusted Error for this ADC, but seems to fall outside of the ~6bit error range for offset.

We have approximately 5 samples of the circuit constructed, with all samples showing a consistent error of about 6 bits low.

We will attempt to buffer the output of the LTC1966 to get a lower impedance output, but do not feel that this is the root of the issue.

Are there other things that we should explore? Or is this simply within the expected error of the ADC.