Part Number: LDC1612

Other Parts Discussed in Thread: MSP430FR5739

INTB will not de-assert(it's always logic low) which prevents the microprocessor from reading of data from DATA0_MSB and DATA0_LSB. We've checked the microprocessor code and if we disconnect the INTB pin and we trigger the input INTB is connected to with a push button the code executes correctly and the interrupt is called and the DATA0_ MSB and DATA0_LSB are read, this leads us to believe we've done something wrong with the LDC config but it seems straight forward.

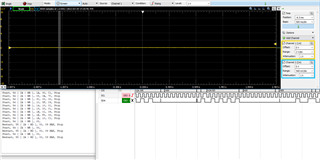

We've hooked a scope up to the INTB pin and triggered reading of DATA0_MSB and then DATA0_LSB and INTB didn't change state. We've also tried reading the Status register 0x18 to see if that would cause INTB to de-assert it didn't. The value in 0x18 is 0x48 which according to the data sheet is the Data Ready Flag and the Channel0 Unread Conversion, which seems correct.

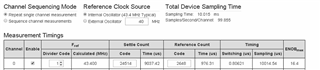

The LDC registers are set up with the following write commands from the microprocessor in the order below

| Register | Address | Value |

| CONFIG | 0x1A | 0x30C1 |

| RCOUNT0 | 0x08 | 0x0A7C |

| OFFSET0 | 0x0C | 0x0000 |

| SETTLECOUNT0 | 0x10 | 0x5Fhe |

| CLOCK_DIVIDER0 | 0x14 | 0x1001 |

| ERROR_CONFIG | 0x19 | 0x0001 |

| MUX_CONFIG | 0x1B | 0x0209 |

| DRIVE_CURRENT0 | 0x1E | 0xF800 |

| CONFIG | 0x1A | 0x10C1 |

Any thoughts about what is causing the INTB signal to always be asserted? For reference we are using a MSP430FR5739 as the microprocessor and the connected pin is set as an input with no pull up/down resistor and P1IES = 1 so the interrupt triggers on the high to low transition. We also tried it with the P1IES set to 0 just to see what happens and had the same result of INTB always asserted