Hi Team,

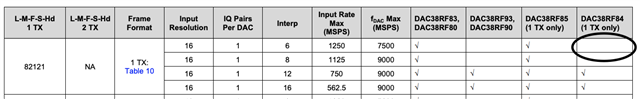

Could you please check the below customer error codes to make sure i'm 100% correct. Customer is evaluating DAC38RF84, and is testing using LMFSHd = 82121, interpolation 6x, 8x. From table 44 of the datasheet this configuration is not supported so i believe this is causing the error codes and they need to move to the RF80.

Error codes below:

"DAC A, Lane 0 code synchronization error"

"DAC A, Lane 0 8b/10b not-in-table code error"

"DAC A, Lane 0 8b/10b disparity error"

"DAC A, Lane 0 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 1 code synchronization error"

"DAC A, Lane 1 8b/10b not-in-table code error"

"DAC A, Lane 1 8b/10b disparity error"

"DAC A, Lane 1 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 2 code synchronization error"

"DAC A, Lane 2 8b/10b not-in-table code error"

"DAC A, Lane 2 8b/10b disparity error"

"DAC A, Lane 2 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 3 code synchronization error"

"DAC A, Lane 3 8b/10b not-in-table code error"

"DAC A, Lane 3 8b/10b disparity error"

"DAC A, Lane 3 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 4 code synchronization error"

"DAC A, Lane 4 8b/10b not-in-table code error"

"DAC A, Lane 4 8b/10b disparity error"

"DAC A, Lane 4 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 5 code synchronization error"

"DAC A, Lane 5 8b/10b not-in-table code error"

"DAC A, Lane 5 8b/10b disparity error"

"DAC A, Lane 5 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 6 code synchronization error"

"DAC A, Lane 6 8b/10b not-in-table code error"

"DAC A, Lane 6 8b/10b disparity error"

"DAC A, Lane 6 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 7 code synchronization error"

"DAC A, Lane 7 8b/10b not-in-table code error"

"DAC A, Lane 7 8b/10b disparity error"

"DAC A, Lane 7 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

Additionally, i think there's an error in the datasheet which has caused the customer to select the wrong device. On Page 6 the overview states the RF84 can support 6x interpolation, but in table 9 P44 there is no option for the RF84 with 6x interpolation. Can you please check and confirm table 44 is correct.

Thanks and best regards,

Dan