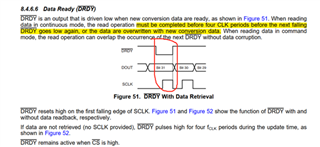

My question is as follows:Using FPGA to communicate with ads1283 to collect analog signal,After downloading the parameters, the timing of drdy and SCLK is inconsistent with the manual。

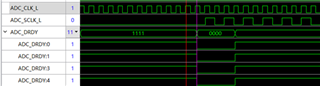

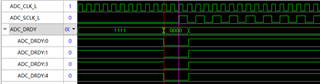

The following two figures are shown,Normally, drdy signal only contains one SCLK waveform, but occasionally in my timing, a drdy signal contains two SCLK waveforms. This will result in the data I collected being sometimes correct and sometimes twice as small。

Parameter:sclk2.048MHZ,clk4.096MHZ

The following figure contains the timing of CLK, SCLK and drdy signals(One right, one error)

Please kindly give your advice.

Best Regard