Other Parts Discussed in Thread: DAC39J84, TSW14J57EVM

Hi,

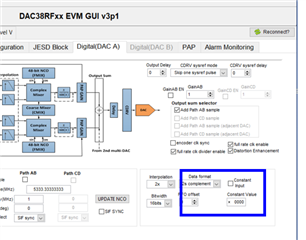

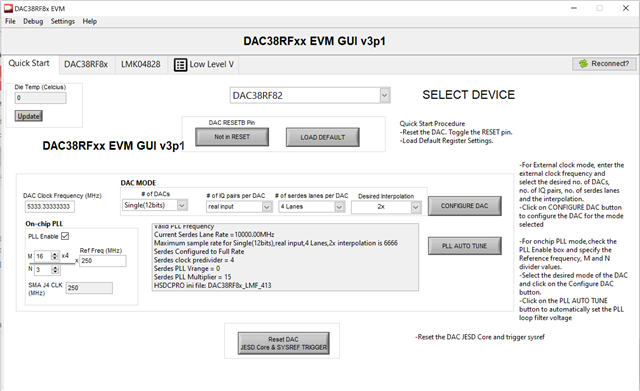

I have configured the DAC38RF82EVM using GUI. we are using CMODE3, with PLL frequency =250MHz.

# of DACs = Single (12bits)

# of IQ pairs per DAC = real input

# of serdes lane per DAC = 4 lanes

Desired Interpolation= X2

GUI Quick Configurations:

"Valid PLL Frequency

Current Serdes Lane Rate =10000.00MHz

Maximum sample rate for Single(12bits),real input,4 Lanes,2x interpolation is 6666

Serdes Configured to Full Rate

Serdes clock predivider = 4

Serdes PLL Vrange = 0

Serdes PLL Multiplier = 15

HSDCPRO ini file: DAC38RF8x_LMF_413"

We have also observed that PLL LF Voltage = 4.

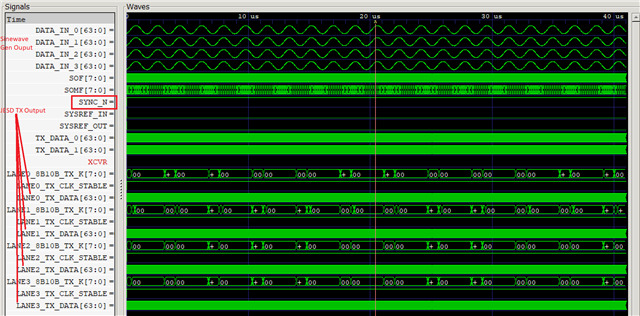

We have observed that, we have correctly received SYNC0B (High) from JESD204B RX of DAC38RF82EVM.

I have attached PPT of GUI configurations.

Are we Configuring DAC38RF82EVM correctly. Please check and let us know, if you find anything wrong.

Thanks,

Imran