Hello,

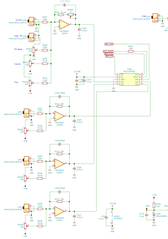

I'm using the ADC124S051 connected to an FPGA and running at the maximum 8MHz clock rate to convert 4 different signal sources in a continuous round-robin cycle. I am seeing noticeable crosstalk between the multiplexed inputs, where the results of the immediately prior conversion are affecting the current conversion. I have tried an number of approaches to fix this:

1) Slowing down the sample rate from 500kSPS to 375kSPS - didn't help.

2) Stalling the SPI clock during the sample acquisition period by several microseconds to extend the settling time - didn't help.

3) Introducing long periods of /CS de-asserted (high) to separate the conversions - didn't help.

4) doing two successive conversions per channel and only using the 2nd result - the 2nd result is still contaminated.

The only thing I've found that prevents crosstalk between the channels is to not change the mux setting - only convert one input channel continuously. That prevents crosstalk but of course doesn't allow me to sample all four channels as my system requires.

I am driving the ADC inputs directly with low impedance op-amp outputs, and I also have 0.01uF caps near the pins to serve as charge reservoirs for the sampling process. I have confirmed with bench DMM measurements that the analog voltages into the ADC are not affecting each other externally.

Are there any suggestions for how I might solve this problem?

Thanks,

Eric