Hi Experts,

I have a question regarding below spec.

This spec requires SCLK falls 10ns before SYNC falls. Can be SCLK negated at the same timing of SYNC falling edge as below?

regards,

Uchikoshi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Experts,

I have a question regarding below spec.

This spec requires SCLK falls 10ns before SYNC falls. Can be SCLK negated at the same timing of SYNC falling edge as below?

regards,

Uchikoshi

Hi,

SCLK and SYNC cannot be changed simultaneously for this device, there is min 10ns required . Idle state of SCLK can be high or low and data is sampled on falling edge of SCLK, which corresponds to SPI mode 1 and mode 1 operation.

Regards,

AK

Hi AK,

Please let me confirm again. Below is the timing where we are applying to DAC7562. We can meet the spec t(1) but SCLK rising edge and SYNC falling edge is the same timing since these signal are generated by the same clock source of internal FPGA.

With this wave form, DAC does not output anything. So we are asking this question. Should we modify the SYNC timing shown in above?

Regards,

Uchikoshi

Hi

How many SCLK falling edge are you providing before you take /SYNC high in the SPI frame? we need min 24 SCLK falling edges for the DAC to accept the commands.

You can delay the /SYNC as per the diagram and give min 24 SCLK fall edge.

Can you post one complete SPI frame? ( SYNC, SCLK and SDI)

Regards,

AK

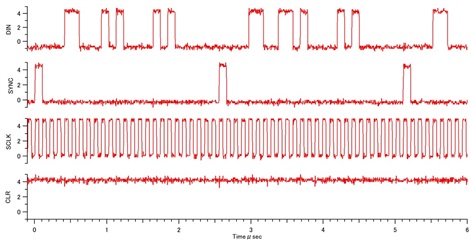

Below is one complete SPI flame.

Can you see something wrong other than SYNC assert timing?

Regards,

Uchikoshi

Hi,

This frame looks fine to me ( are you sending 0x18, 0xA1, 0x40)

What is the SCLK frequency here? And SYNC high time?

Are you maintaining timing t5?

Regards,

AK