Other Parts Discussed in Thread: ADS1274,

Hello TI Community,

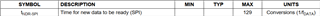

I have a simple question about the table 10 of the ADS1274/8 datasheet.

Does it mean that the /DRDY settle time is 129 * (1 / Fdata)?

e.g. for Fdata = 1kHz => tNDR-SPI = 129ms

Thanks for your help.

Best Regards

Benjamin Nordman