Hi Team,

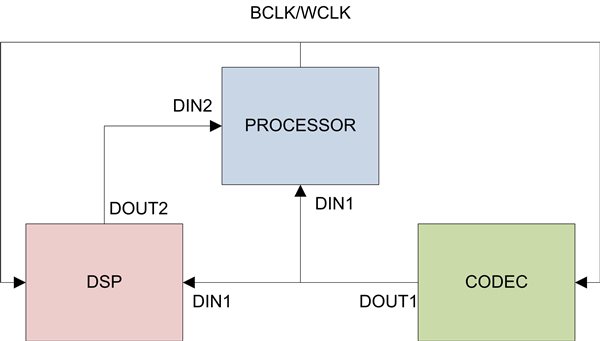

In a system with three devices, lets say a CODEC, Audio DSP (C55x) and another processor, if the processor is the I2S master device, can the DSP and CODEC communicate independently of the ARM9, assuming they are slaves? In other words, how would the communication take place between the DSP and the CODEC assuming that the processor is the master?

I am familiar with I2C, SPI and other comm. topologies but not so much I2S. In the case of I2C and SPI, I know that the communication is controlled by the master...so such configuration would not be possible unless routed through the master. Is the same true for I2S?

Assuming this is not possible and there will be multiple master devices, what steps must be taken to mitigate synchronization issues if trying to mix audio data from both masters in one slave for example?

Thanks in advance,