Other Parts Discussed in Thread: ADC12J4000, ADC12J4000EVM

e2e,

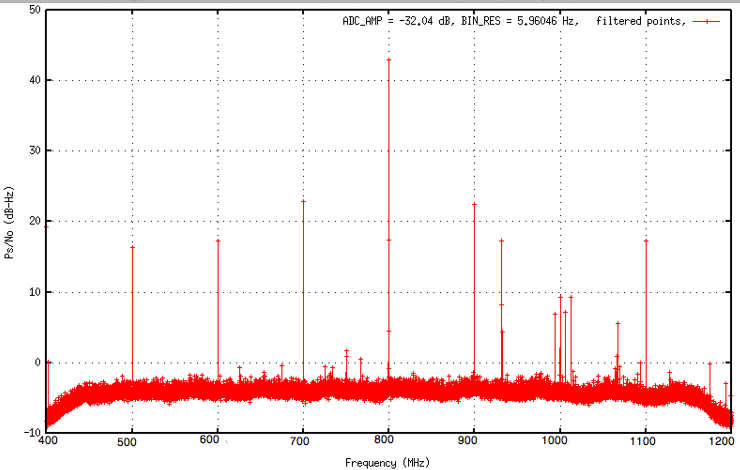

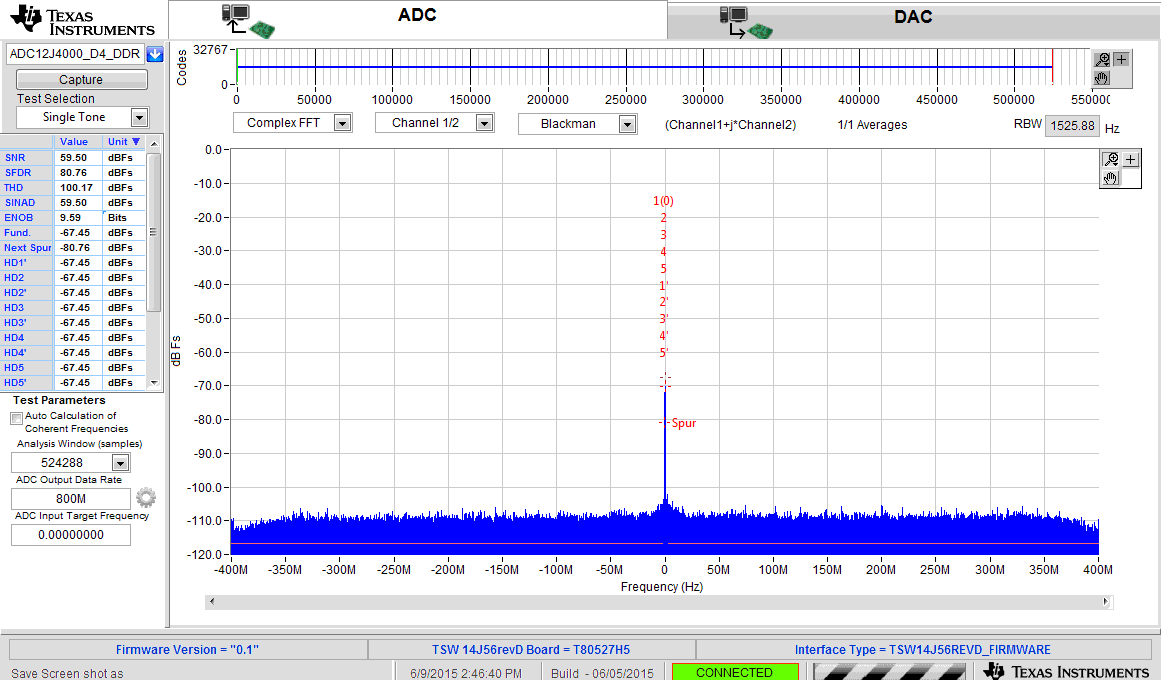

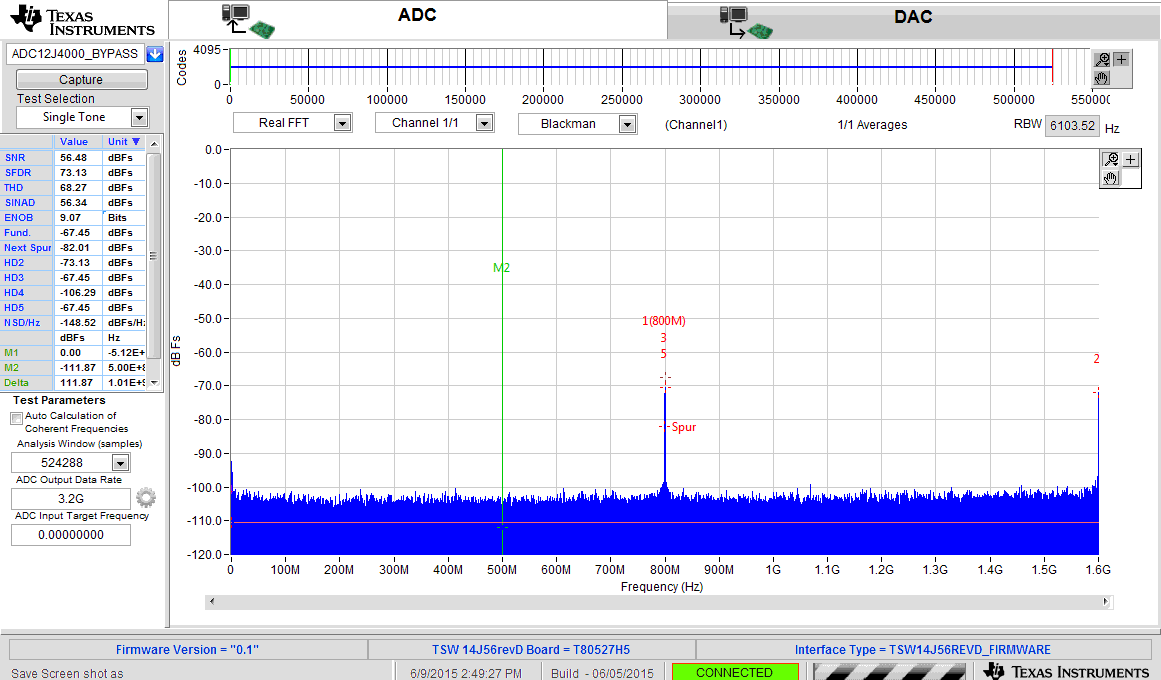

We have a customer that has noticed that the ADC12J4000 has a strong interleave spur at ¼ of the sampling frequency in DDC mode. In normal mode, the interleave spur can be reduced significant by enabling the timing calibration mode. Attached plot please find the acquired ADC spectrum from white noise input.

The test setup:

3.2GHz sampling rate

Decimation = 4

P54 = 1 (L = 4)

NCO = -800MHz (2.4GHz)

DDC gain off

Please explain the reason the DDC adds this spur.

Thanks for your help.

Regards,

John Wiemeyer

//---- Dumping ADC12J4000 Registers --------- Addr Data Name ADC12J4000 #1 0x000 0x3C Cfg_A 0x001 0x00 Cfg_B 0x002 0x00 Device configuration 0x003 0x03 Chip type = 0x03 0x006 0x03 Chip version = 0x03 0x00C 0x51 Vender ID = 0x51 0x00D 0x04 Vender ID = 0x04 0x010 0x00 SPI configuration 0x021 0x00 Power on reset 0x022 0x40 I/O gain 0 0x023 0x00 I/O gain 1 0x025 0x40 I/O offset 0 0x026 0x00 I/O offset 1 0x030 0xC0 Clock generator control 0 0x031 0xC7 Clock generator status 0x032 0x80 Clock generator control 2 0x033 0xC3 Analog miscellaneous 0x034 0x2F Input clamp enable 0x040 0x04 Serializer configuration 0x050 0x06 Calibration configuration 0 0x051 0xF4 Calibration configuration 1 0x057 0x10 Calibration background control 0x058 0x00 ADC pattern and over-range enable 0x05A 0x00 Calibration vector 0x05B 0x0F Calibration status 0x066 0x03 Timing calibration 0x200 0x32 Digital down-converter (DDC) control 0x201 0x7F JESD204B control 1 0x202 0x80 JESD204B control 2 0x203 0x00 JESD204B Device ID 0x204 0x00 JESD204B control 3 0x205 0x7C JESD204B status [6] link up; [5]: sync~ deasserted; [4] realigned; [3] aligned; [2] pll_locked 0x206 0xF2 Over-range control 0 0x207 0xAB Over-range control 1 0x208 0x00 Over-range period 0x20C 0x01 DDC configuration preset mode 0x20D 0x00 DDC configuration preset select 0x20E 0x00 NCO_RDIV[7:0] 0x20F 0x00 NCO_RDIV[15:8] 0x210 0x00 NCO_FREQ_0[7:0] 0x211 0x00 NCO_FREQ_0[15:8] 0x212 0x00 NCO_FREQ_0[23:16] 0x213 0xE0 NCO_FREQ_0[31:24] 0x214 0x00 NCO_PHASE_0[7:0] 0x215 0x00 NCO_PHASE_0[15:8] 0x216 0xFF DDC_DLY_0 0x218 0x00 NCO_FREQ_1[7:0] 0x219 0x00 NCO_FREQ_1[15:8] 0x21A 0x00 NCO_FREQ_1[23:16] 0x21B 0x80 NCO_FREQ_1[31:24] 0x21C 0x00 NCO_PHASE_1[7:0] 0x21D 0x00 NCO_PHASE_1[15:8] 0x21E 0xFF DDC_DLY_1 0x220 0x00 NCO_FREQ_2[7:0] 0x221 0x00 NCO_FREQ_2[15:8] 0x222 0x00 NCO_FREQ_2[23:16] 0x223 0x40 NCO_FREQ_2[31:24] 0x224 0x00 NCO_PHASE_2[7:0] 0x225 0x00 NCO_PHASE_2[15:8] 0x226 0xFF DDC_DLY_2 0x228 0x00 NCO_FREQ_3[7:0] 0x229 0x00 NCO_FREQ_3[15:8] 0x22A 0x00 NCO_FREQ_3[23:16] 0x22B 0x20 NCO_FREQ_3[31:24] 0x22C 0x00 NCO_PHASE_3[7:0] 0x22D 0x00 NCO_PHASE_3[15:8] 0x22E 0xFF DDC_DLY_3 0x230 0x00 NCO_FREQ_4[7:0] 0x231 0x00 NCO_FREQ_4[15:8] 0x232 0x00 NCO_FREQ_4[23:16] 0x233 0x10 NCO_FREQ_4[31:24] 0x234 0x00 NCO_PHASE_4[7:0] 0x235 0x00 NCO_PHASE_4[15:8] 0x236 0xFF DDC_DLY_4 0x238 0x00 NCO_FREQ_5[7:0] 0x239 0x00 NCO_FREQ_5[15:8] 0x23A 0x00 NCO_FREQ_5[23:16] 0x23B 0x08 NCO_FREQ_5[31:24] 0x23C 0x00 NCO_PHASE_5[7:0] 0x23D 0x00 NCO_PHASE_5[15:8] 0x23E 0xFF DDC_DLY_5 0x240 0x00 NCO_FREQ_6[31:24] 0x241 0x00 NCO_FREQ_6[23:16] 0x242 0x00 NCO_FREQ_6[15:8] 0x243 0x04 NCO_FREQ_6[7:0] 0x244 0x00 NCO_PHASE_6[7:0] 0x245 0x00 NCO_PHASE_6[15:8] 0x246 0xFF DDC_DLY_6 0x248 0x00 NCO_FREQ_7[31:24] 0x249 0x00 NCO_FREQ_7[23:16] 0x24A 0x00 NCO_FREQ_7[15:8] 0x24B 0x00 NCO_FREQ_7[7:0] 0x24C 0x00 NCO_PHASE_7[7:0] 0x24D 0x00 NCO_PHASE_7[15:8] 0x24E 0xFF DDC_DLY_7 ADC12J4000 #2 0x000 0x3C Cfg_A 0x001 0x00 Cfg_B 0x002 0x00 Device configuration 0x003 0x03 Chip type = 0x03 0x006 0x03 Chip version = 0x03 0x00C 0x51 Vender ID = 0x51 0x00D 0x04 Vender ID = 0x04 0x010 0x00 SPI configuration 0x021 0x00 Power on reset 0x022 0x40 I/O gain 0 0x023 0x00 I/O gain 1 0x025 0x40 I/O offset 0 0x026 0x00 I/O offset 1 0x030 0xC0 Clock generator control 0 0x031 0xC7 Clock generator status 0x032 0x80 Clock generator control 2 0x033 0xC3 Analog miscellaneous 0x034 0x2F Input clamp enable 0x040 0x04 Serializer configuration 0x050 0x06 Calibration configuration 0 0x051 0xF4 Calibration configuration 1 0x057 0x10 Calibration background control 0x058 0x00 ADC pattern and over-range enable 0x05A 0xC9 Calibration vector 0x05B 0x0B Calibration status 0x066 0x03 Timing calibration 0x200 0x32 Digital down-converter (DDC) control 0x201 0x7F JESD204B control 1 0x202 0x80 JESD204B control 2 0x203 0x00 JESD204B Device ID 0x204 0x00 JESD204B control 3 0x205 0x7C JESD204B status [6] link up; [5]: sync~ deasserted; [4] realigned; [3] aligned; [2] pll_locked 0x206 0xF2 Over-range control 0 0x207 0xAB Over-range control 1 0x208 0x00 Over-range period 0x20C 0x01 DDC configuration preset mode 0x20D 0x00 DDC configuration preset select 0x20E 0x00 NCO_RDIV[7:0] 0x20F 0x00 NCO_RDIV[15:8] 0x210 0x00 NCO_FREQ_0[7:0] 0x211 0x00 NCO_FREQ_0[15:8] 0x212 0x00 NCO_FREQ_0[23:16] 0x213 0xE0 NCO_FREQ_0[31:24] 0x214 0x00 NCO_PHASE_0[7:0] 0x215 0x00 NCO_PHASE_0[15:8] 0x216 0xFF DDC_DLY_0 0x218 0x00 NCO_FREQ_1[7:0] 0x219 0x00 NCO_FREQ_1[15:8] 0x21A 0x00 NCO_FREQ_1[23:16] 0x21B 0x80 NCO_FREQ_1[31:24] 0x21C 0x00 NCO_PHASE_1[7:0] 0x21D 0x00 NCO_PHASE_1[15:8] 0x21E 0xFF DDC_DLY_1 0x220 0x00 NCO_FREQ_2[7:0] 0x221 0x00 NCO_FREQ_2[15:8] 0x222 0x00 NCO_FREQ_2[23:16] 0x223 0x40 NCO_FREQ_2[31:24] 0x224 0x00 NCO_PHASE_2[7:0] 0x225 0x00 NCO_PHASE_2[15:8] 0x226 0xFF DDC_DLY_2 0x228 0x00 NCO_FREQ_3[7:0] 0x229 0x00 NCO_FREQ_3[15:8] 0x22A 0x00 NCO_FREQ_3[23:16] 0x22B 0x20 NCO_FREQ_3[31:24] 0x22C 0x00 NCO_PHASE_3[7:0] 0x22D 0x00 NCO_PHASE_3[15:8] 0x22E 0xFF DDC_DLY_3 0x230 0x00 NCO_FREQ_4[7:0] 0x231 0x00 NCO_FREQ_4[15:8] 0x232 0x00 NCO_FREQ_4[23:16] 0x233 0x10 NCO_FREQ_4[31:24] 0x234 0x00 NCO_PHASE_4[7:0] 0x235 0x00 NCO_PHASE_4[15:8] 0x236 0xFF DDC_DLY_4 0x238 0x00 NCO_FREQ_5[7:0] 0x239 0x00 NCO_FREQ_5[15:8] 0x23A 0x00 NCO_FREQ_5[23:16] 0x23B 0x08 NCO_FREQ_5[31:24] 0x23C 0x00 NCO_PHASE_5[7:0] 0x23D 0x00 NCO_PHASE_5[15:8] 0x23E 0xFF DDC_DLY_5 0x240 0x00 NCO_FREQ_6[31:24] 0x241 0x00 NCO_FREQ_6[23:16] 0x242 0x00 NCO_FREQ_6[15:8] 0x243 0x04 NCO_FREQ_6[7:0] 0x244 0x00 NCO_PHASE_6[7:0] 0x245 0x00 NCO_PHASE_6[15:8] 0x246 0xFF DDC_DLY_6 0x248 0x00 NCO_FREQ_7[31:24] 0x249 0x00 NCO_FREQ_7[23:16] 0x24A 0x00 NCO_FREQ_7[15:8] 0x24B 0x00 NCO_FREQ_7[7:0] 0x24C 0x00 NCO_PHASE_7[7:0] 0x24D 0x00 NCO_PHASE_7[15:8] 0x24E 0xFF DDC_DLY_7