Part Number: ADS54J60

Other Parts Discussed in Thread: ADS54J40, , LMH6401, TSW54J60EVM

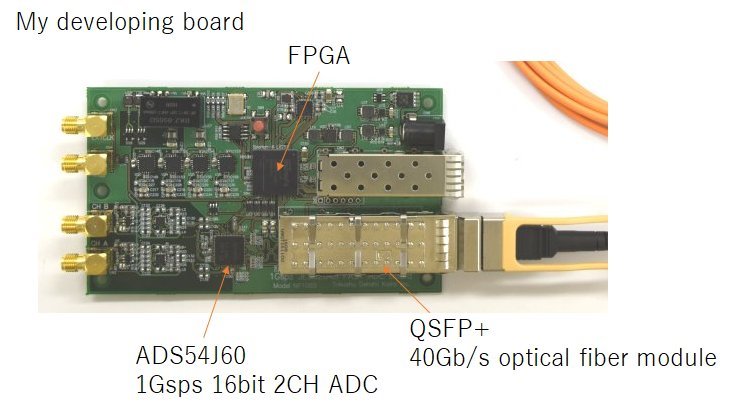

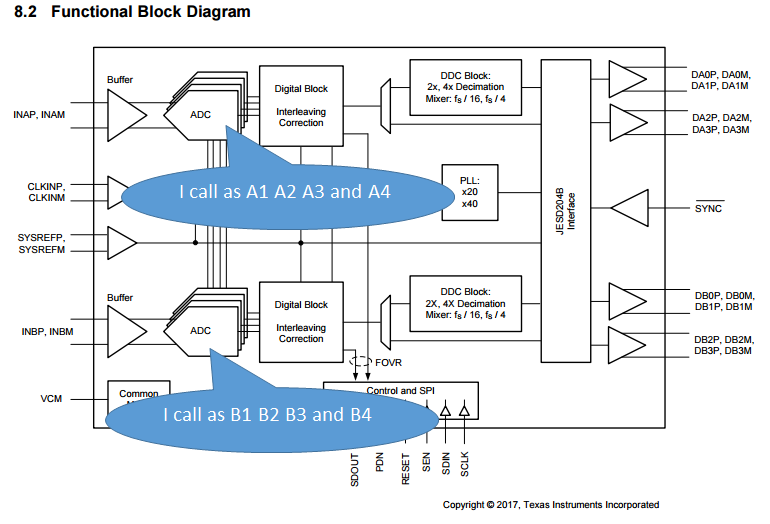

I am developing an 1Gsps ADC board using ADS54J60.

It sends data by JESD204B using optical fiber.

The operation of JESD204B is going well.

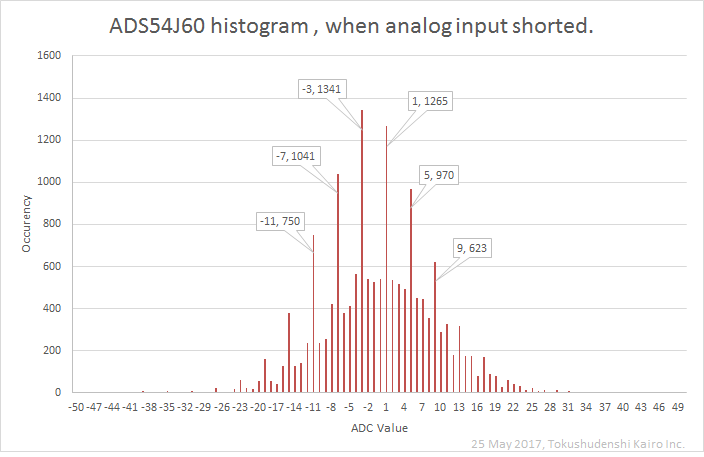

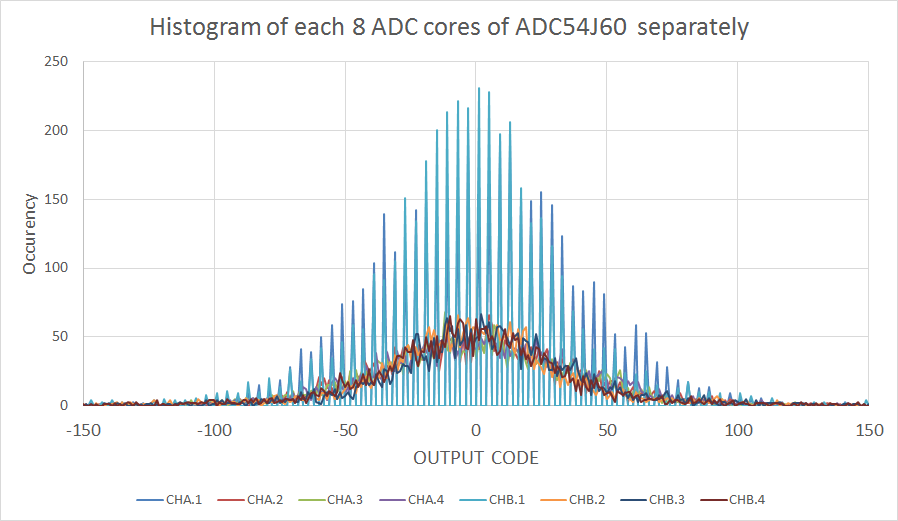

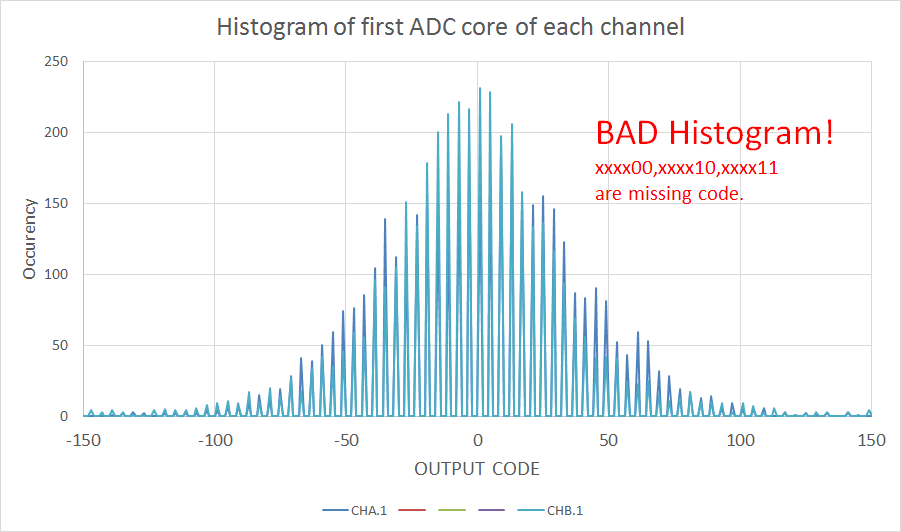

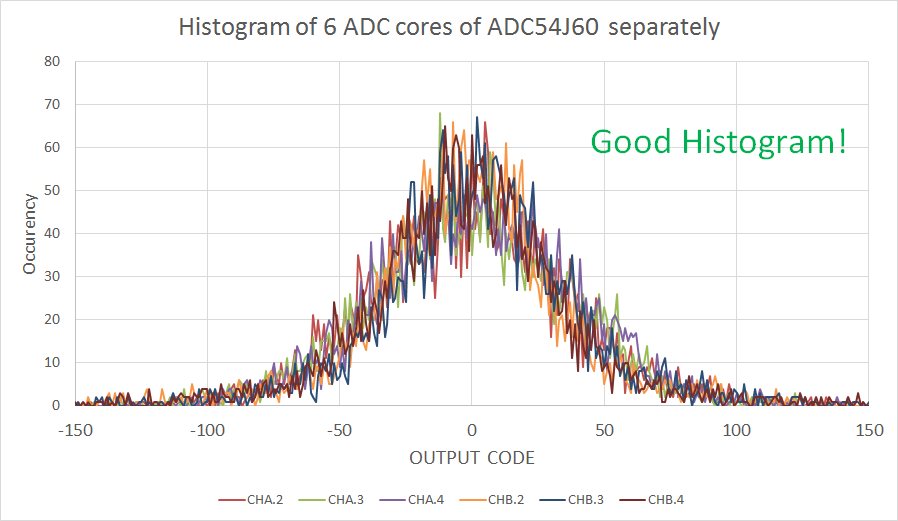

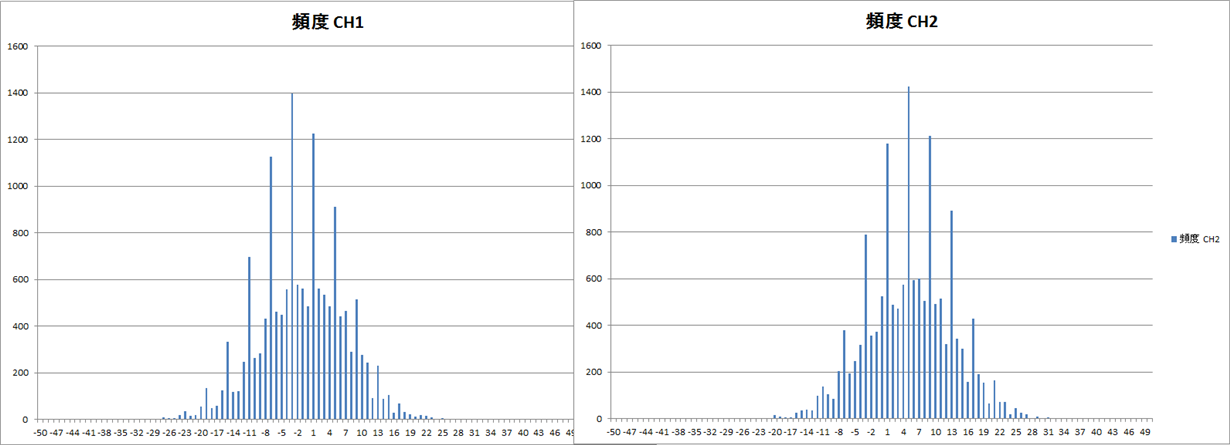

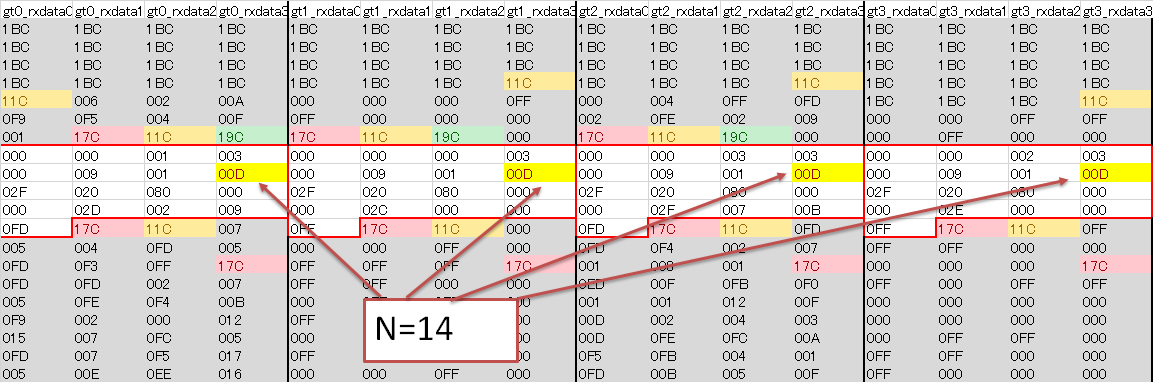

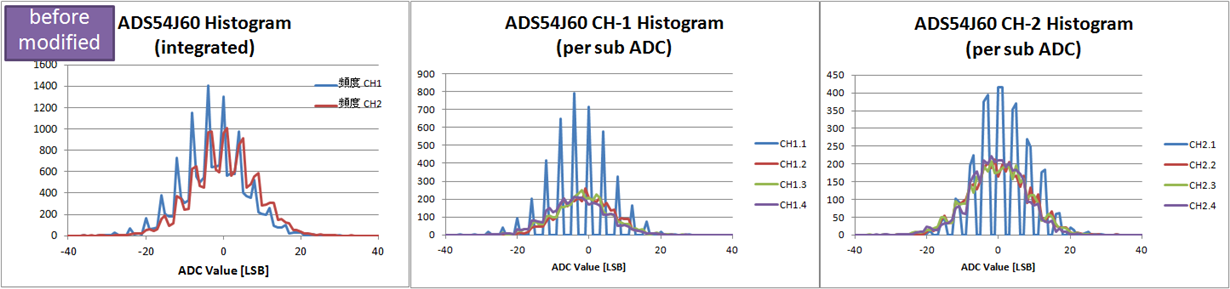

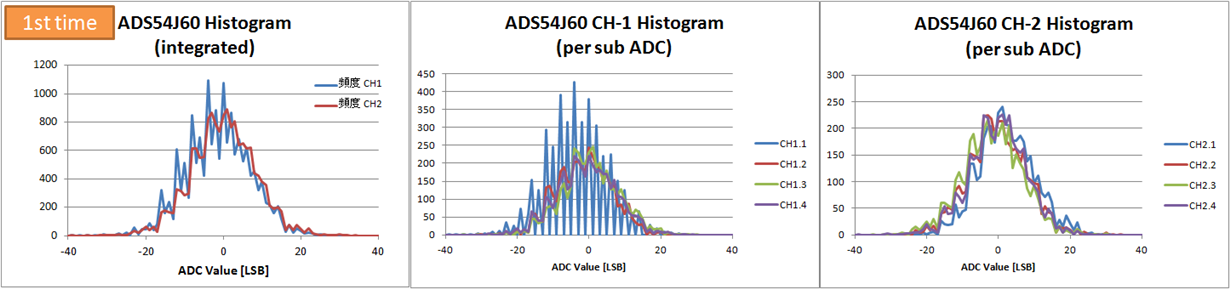

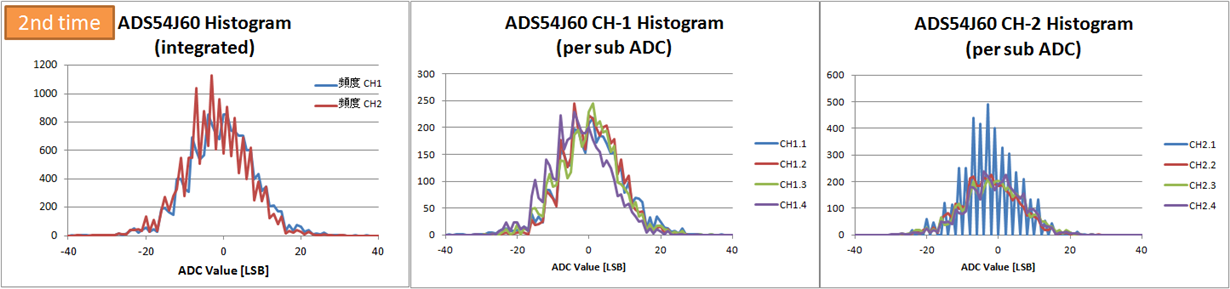

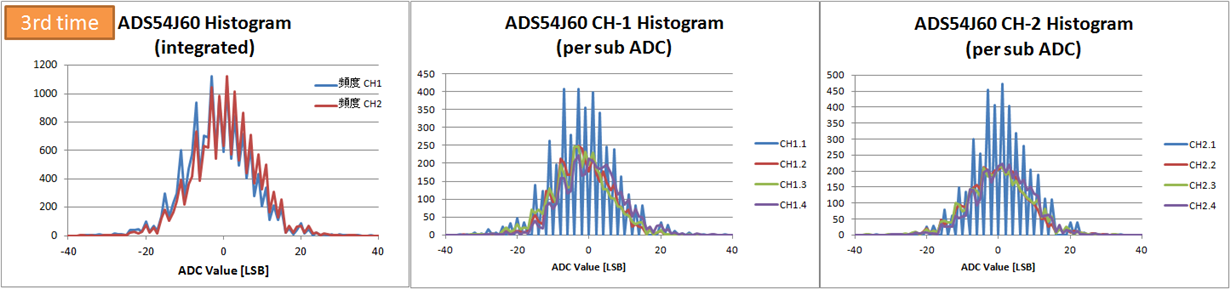

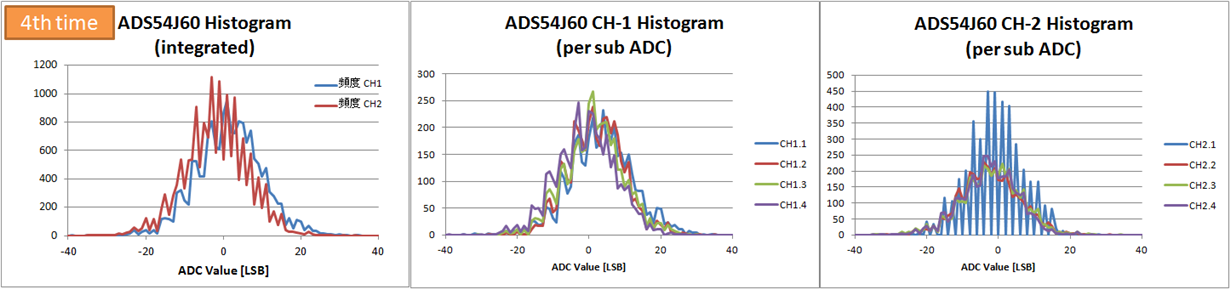

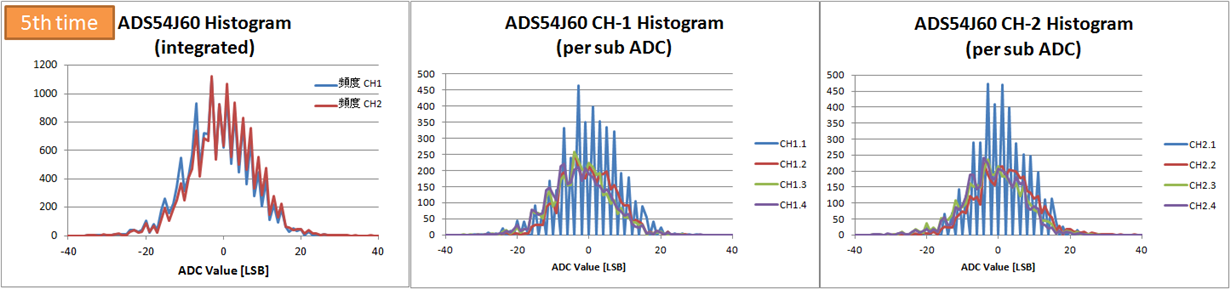

Taking a code histogram at the input voltage difference is 0, it was like a comb !

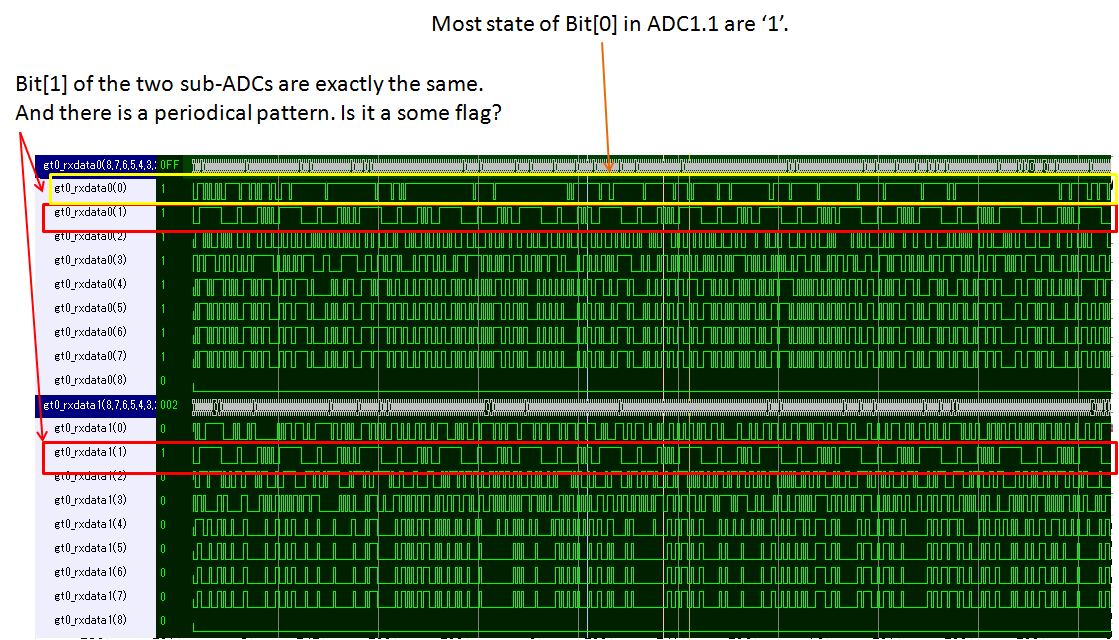

When the least significant bit of the ADC code is "01", it seems to be larger.

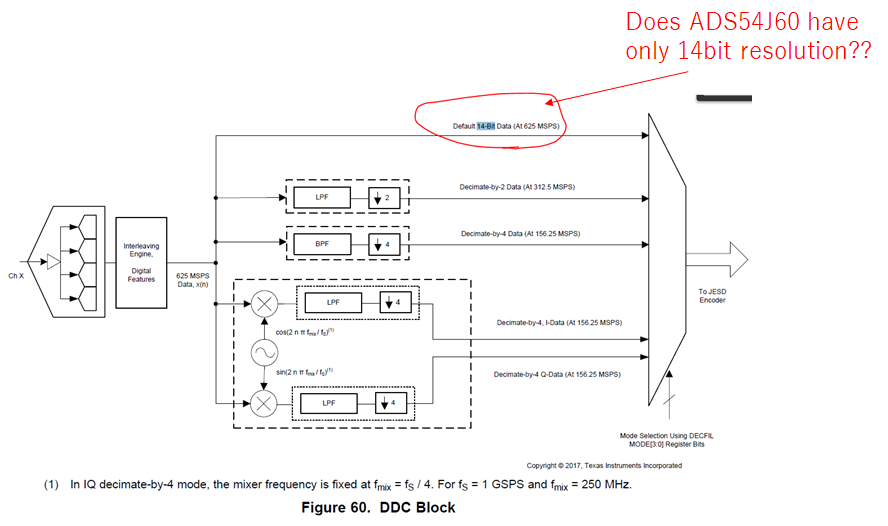

According to the datasheet there is a description "Default 14-Bit Data" on Fig.60.

Does ADS54J60 have only 14bit resolution??

Condition is following.

LMFS config is 4211.

K=16

N=5

SYSREF=1.953125MHz ( = 1GHz / 32 / 16)

Please tell me the reason for this.

Best regards,

Ryuji Naitou