Part Number: DLPLCRDC4422EVM

Hi TI team,

Is it able to program our own 2.7K pattern into DLPLCRDC4422EVM? How does it work?

We'd like to display the native pixel through this way, due to EDID standard limitation.

Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DLPLCRDC4422EVM

Hi TI team,

Is it able to program our own 2.7K pattern into DLPLCRDC4422EVM? How does it work?

We'd like to display the native pixel through this way, due to EDID standard limitation.

Thanks.

If you input the native DMD resolution, it should pass through without XPR. i.e. For the DLP470TE, if you input 1920x1080, it should pass through 1920x1080. If you input UHD, XPR will be applied.

Please be sure to download the firmware package for the DMD you plan to use. Inside that package, there is a xls file with the supported Vx1 input resolutions and timings; the supported timings are different for the 470TE and 660TE DMDs.

Thank you for help, Gary

I download the firmware package for DLP660TE. The Excel file shows the resolution is 2712x1528, but DMD datasheet indicates native resolution is 2716x1528. Please help to check which one is correct resolution for input?

2712 x 1528 for the Vx1 input is correct. I believe that difference is due to a Vx1 implementation limitation.

We've tried 4K input image seems workable, but while 2.7K image be input (which should be passed through w/o XPR), it still failed.

So would like to know can TI composer or any other functions read the pixel starting positions and timing of input signal which output from Vby1? How does it work?

It would be much helpful if you have any other advise.

Thank you.

Jackie,

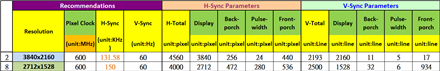

Are you using one of the specific timings supported w/ Vx1 pixel clock @ 600MHz?

Regards,

Gary

| DLP660TE Recommended Video Timings for fixed 600Mhz pix clk, 8-channel Vx1 | ||||||||||||||

| Recommendations | H-Sync Parameters | V-Sync Parameters | ||||||||||||

| Resolution | Pixel Clock | H-Sync | V-Sync | H-Total | Display | Back-porch | Pulse-width | Front-porch | V-Total | Display | Back-porch | Pulse-width | Front-porch | |

| (unit:MHz) | (unit:KHz) | (unit:Hz) | unit:pixel | unit:pixel | unit:pixel | unit:pixel | unit:pixel | unit:Line | unit:line | unit:line | unit:line | unit:line | ||

| 1 | 3840x2160 | 600 | 110.95 | 50 | 5408 | 3840 | 256 | 32 | 1280 | 2216 | 2160 | 35 | 5 | 16 |

| 2 | 3840x2160 | 600 | 131.58 | 60 | 4560 | 3840 | 256 | 24 | 440 | 2193 | 2160 | 11 | 5 | 17 |

| 3 | 2712x1528 | 600 | 111.11 | 24 | 5400 | 2712 | 472 | 280 | 1936 | 4624 | 1528 | 49 | 6 | 3041 |

| 4 | 2712x1528 | 600 | 111.11 | 25 | 5400 | 2712 | 472 | 280 | 1936 | 4440 | 1528 | 49 | 6 | 2857 |

| 5 | 2712x1528 | 600 | 125 | 30 | 4800 | 2712 | 472 | 280 | 1336 | 4160 | 1528 | 32 | 6 | 2594 |

| 6 | 2712x1528 | 600 | 147.35 | 48 | 4072 | 2712 | 472 | 280 | 608 | 3070 | 1528 | 32 | 6 | 1504 |

| 7 | 2712x1528 | 600 | 150 | 50 | 4000 | 2712 | 472 | 280 | 536 | 3000 | 1528 | 32 | 6 | 1434 |

| 8 | 2712x1528 | 600 | 150 | 60 | 4000 | 2712 | 472 | 280 | 536 | 2500 | 1528 | 32 | 6 | 934 |

| 9 | 2712x1528 | 600 | 185.64 | 96 | 3232 | 2712 | 100 | 100 | 320 | 1933 | 1528 | 49 | 6 | 350 |

| 10 | 2712x1528 | 600 | 185.64 | 100 | 3232 | 2712 | 100 | 100 | 320 | 1856 | 1528 | 49 | 6 | 273 |

| 11 | 2712x1528 | 600 | 194.81 | 120 | 3080 | 2712 | 164 | 32 | 172 | 1620 | 1528 | 45 | 5 | 42 |

Gary,

Vby1 uses item 2 for 4K input and item 8 for 2.7K input. But we read source information from composer, the data information is different from the timing table. Is any setting needed to do to get correct source information? Thanks

Jackie,

The source information is for the 4422 controllers, not for the FPGA Vx1 input. I do not believe there is a way to see the active Vx1 input timing.

Have you updated the EVM 4422 Flash image per the User Guide instructions? Have you updated the FPGA Flash per the instructions included in DLPC4422 UHD FPGA Programming Guide.pdf, which is included in the DLP660TE firmware package? I suspect these have been updated if you are getting a proper UHD image with a UHD input.

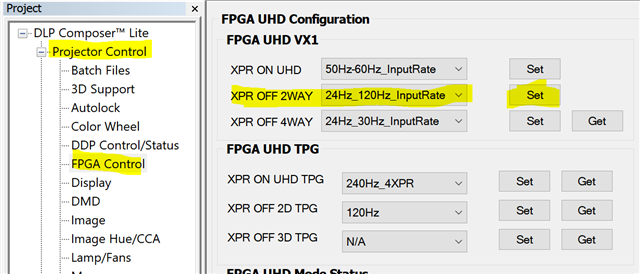

Pleas try setting FPGA UHD VX1 XPR OFF 2WAY in in Projector Control -> FPGA Control.

Regards,

Gary

No, we don't update the flash image. When we set FPGA UHD VX1 XPR OFF 2WAY in FPGA Control, the 4K projected image turns off (no image is projected). I know XPR uses 120Hz for output image, do you think VX1 vendor has to try item 11 of timing table? Are the parameters of timing table set exactly the same? Or the parameters need to adjust a little? Do you suggest how to adjust?

Jackie,

Any of the timings in the xls file should work; they have all been tested. It is important to note that the Vx1 receiver requires a 600MHz Vx1 Pixel clock; it will not work at any other rate.

What versions are reported on the DDP Control/Status and FPGA Control Pages?

Regards,

Gary

Hi Gary,

Thank you for support. We can project 2.7K pattern successfully and turn off XPR manually in FPGA Control page. However, I want to confirm "If you input the native DMD resolution, it should pass through without XPR.", does it mean XPR will be turned off automatically with 2.7K signal input?

Jackie - You need to set the XPR_OFF_2WAY to disable XPR processing in the XPR FPGA (as shown in my previous message).