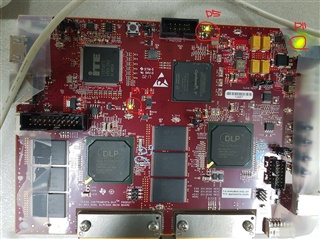

Other Parts Discussed in Thread: DLP9000, TPS65145, DLPC910, DLPC900, , DLPLCRC900DEVM

Dear forum members,

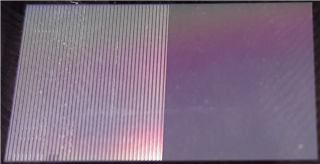

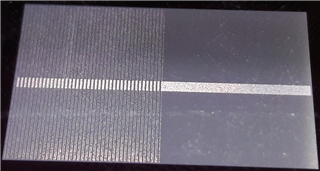

We're having the following issue with our DLP9000 DMD, first half of the image always shows artifacts, it looks like vertical stripes, however it's not homogeneous. In the attached pictures, one image should show only black background, and the other one should show a horizontal white band with black background.

Context:

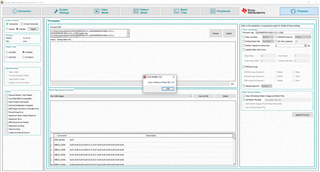

- Board needs to be reset some times before it can stand in normal mode and allows an operation mode to be selected.

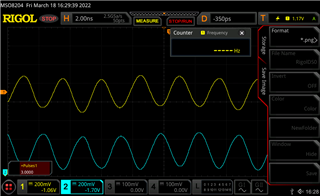

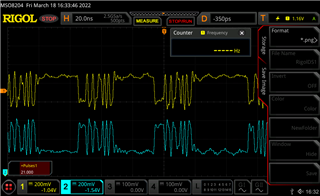

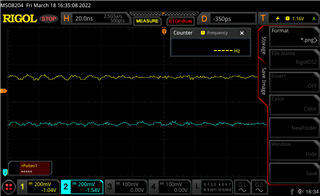

- Even when pattern on the fly mode gets seleceted and sequence gets updated and started, not always can be visualized. This correlates with the voltages generated by the TPS65145 for the DMD in the following way: most of the times TPS65145 shutdowns as soon as it powers on even with enable input high (overload detected?), and sequence is not visualized. When TP65145 can make it to stay on and generates the proper voltages (16V, 8.5V, -10V) then the sequence is visualized.

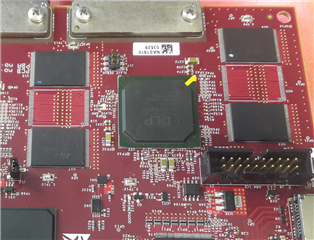

- Master controller gets noticeable hotter than the slave controller (maybe it's related with the half of the image showing the artifacts), I would say it's definitelly overheating.

- The four main regulators on the controller board were already checked (1.8V, 1.1V, 3.3V and 3V).

- The cLGA socket between DMD and PCB was replaced for a new one.

We really appreciate your help.

Marcos.