FPGA model: XC7Z020-1CLG484I4493

DDR3 model: MT41K64M16TW-107: J

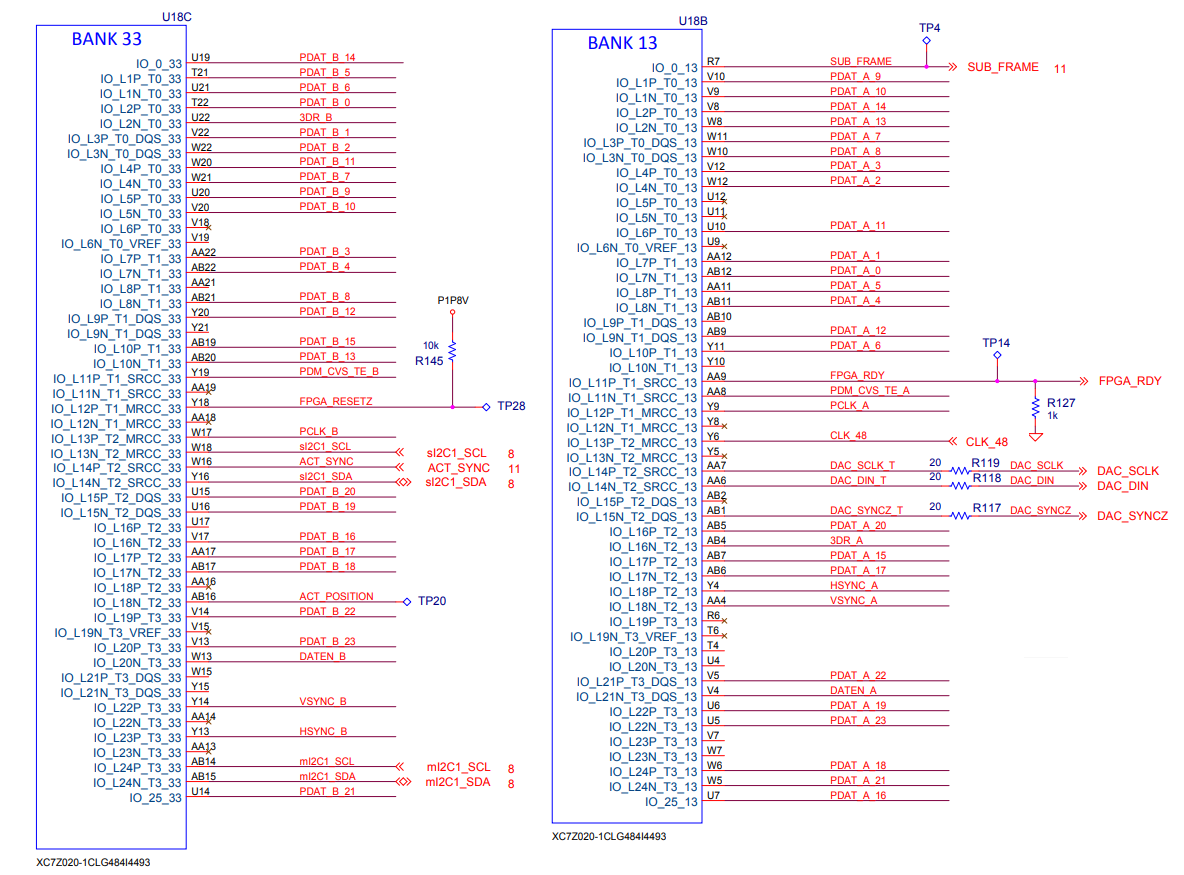

DLPC model: dlpc3437

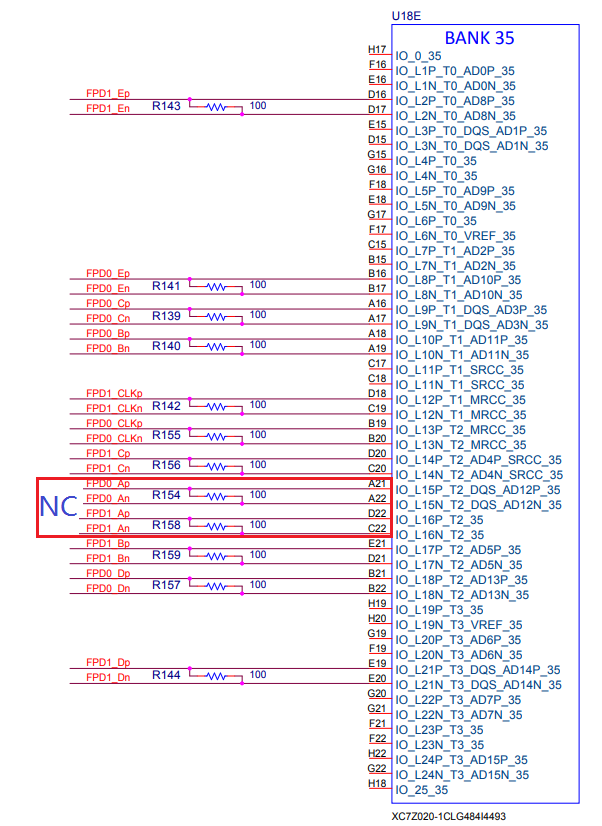

According to the 0.33 male board DLPDLCR3310EVM DISPLAY BOARD cable given by TI, the video input of FPGA uses GM8775C to convert MIPI to dual 8-bit LVDS to drive FPGA, leaving out the lowest bit of each group: FPGA_ AP/AN and FPD0_ AP/AN, as shown in the figure below

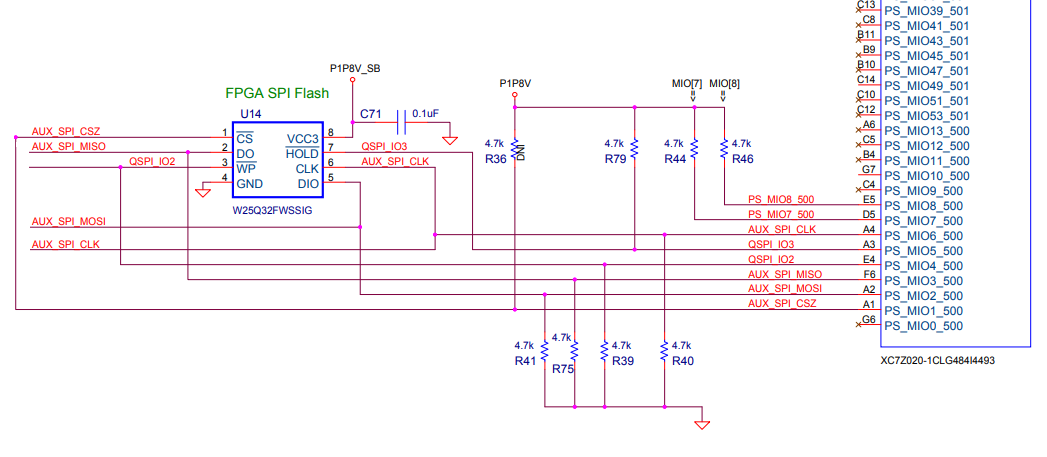

Like the public version, we also use external SPI,

Please provide the corresponding FPGA software (the way to burn FPGA SPI FLASH)