Other Parts Discussed in Thread: DLPDLC-GUI

Dear Sir

When using the new DLP firmware, the FPGA upgrades the DLP pattern firmware through the IIC, but the upgrade fails. The upgrade succeeds when the old DLP firmware is used.

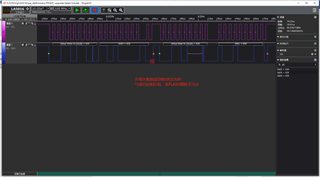

Preliminary location may be the new DLP firmware in E0 erasing D0 flash, DLP erasing incomplete.

Through the program run printing information and IIC signal capture analysis, the following results are obtained;

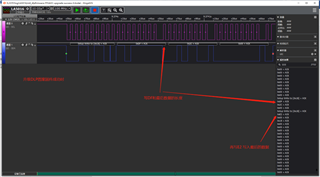

The normal upgrade process is as follows: 1. Write DE D0 to flash data. 2. Write E0 AA BB CC DD to erase the flash, and then read D0 to check the status. 3. Write DE D0 to flash data type. 4. Write DF 00 04 Specifies the length of data to be written to the flash. e1 starts to write data (1024 bytes) and e2 continues to write data over 1024 bytes (the length of data remains 1024 bytes). You need to write another DF length e2 to continue writing data.

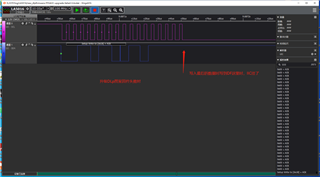

When the upgrade failed, the IIC was suspended during the last phase of writing data.

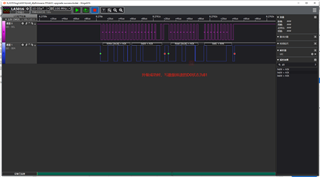

When upgrading the same pattern firmware, using the same FPGA firmware with the new DLP firmware will fail, but using the old DLP firmware will succeed. (That is, the new DLP underlying firmware affects the pattern firmware upgrade function)

Look at the previous return value of D0 read, 0x81 on success, 0x91 on failure, dlpu075a should be incomplete flash erase on failure.

For signal analysis, see the attachments new_dlpfirmware-FPGAIIC-upgrade-failed and old_dlpfirmware-FPGAIIC-upgrade-success.