Hi Team,

Can you please help us with our customer's inquiry below?

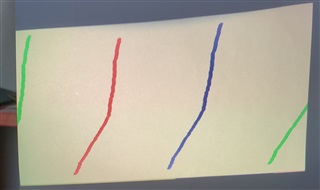

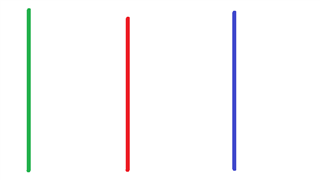

I'm currently working on an application centered around driving a DLPC2607 through a parallel RGB565 interface. In current tests the image is visibly distorted in a way that has me suspect that I am violating one of the timing constraints on the interface. The image I am trying to project is:

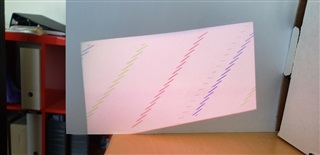

but the image appearing on the projector is:

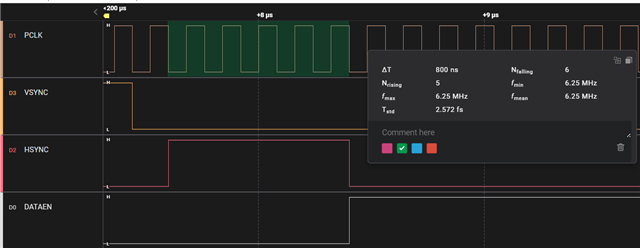

The above image was written to the DLPC2607 with a pixel clock speed of 6.25MHz.

I know that the issue might also be with the file I'm trying to write or the utility I'm using to write it so I'm reaching out to those vendors as well. But the situation does improve/worsen if I halve/double the pixel clock. The image below was written to the DLPC2607 with a pixel clock speed of 3.125MHz:

So there does appear to be some correlation between speed and distortion that has me think this issue may be timing related.

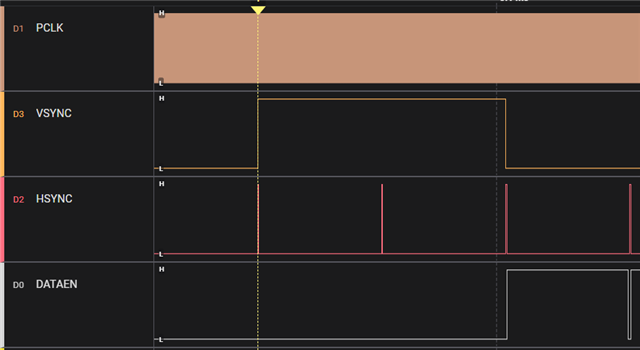

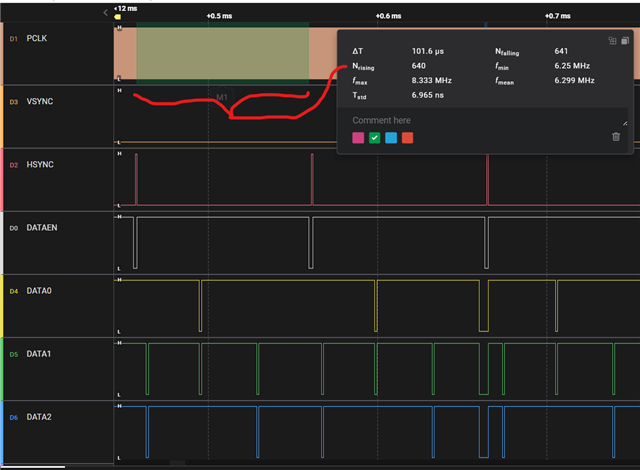

I have attached a logic capture of the PCLK, HSYNC, VSYNC, DATEN and D[0-3] signals. The capture was taken with a Saleae logic analyzer and requires Saleae Logic 2 to open.

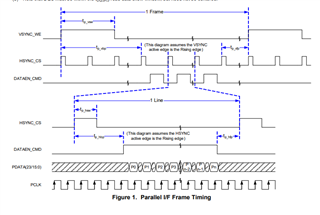

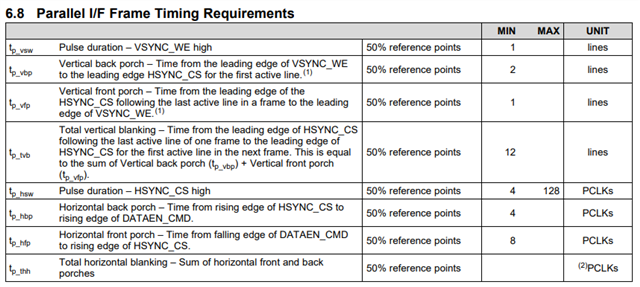

The timing requirements are laid out in the DLPC2607 datasheet in section 6.8

I do believe I am meeting these specs and here's why:

tp_vsw and tp_vpb:

VSYNC is asserted for 2 full lines before valid data is clocked out.

tp_hsw and tp_hpb:

HSYNC is asserted for 5 rising edges before DATAEN is asserted and data is written out

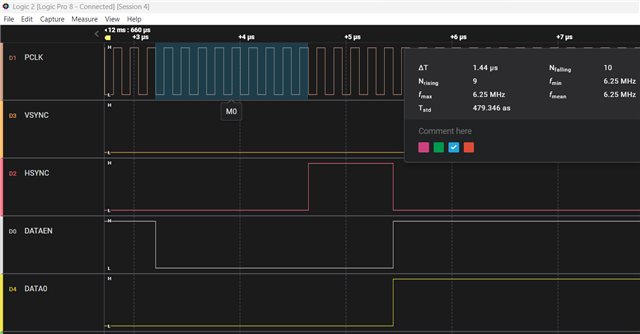

tp_hfp:

There are 9 PCLK cycles between the falling edge of DATAEN and the rising edge of HSYNC.

Furthermore, there are 640 rising PCLK edges per DATAEN i.e. 640 pixels per line being written:

If you're aware of any timing related issue that could cause this behavior I'd be grateful to hear about it.

Regards,

Danilo