I bought your DLP2021LEevm, and then made a similar control board according to your hardware circuit. One piece of the DMD output image on the board we made was invisible. I removed the chip MSP430, and set the enable pins of 3.3V,2.5V,1.0V and 1.8V output from this chip to the logical height. In addition to this, I also found that the current of my board is different from the current of the EVM purchased from TI, my board has 0.2A current while TI's is only 0.08A.

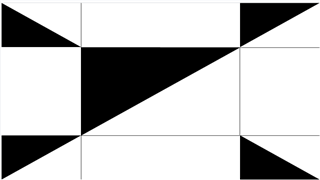

Display image of TI control board

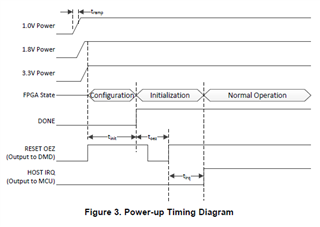

Our board displays images