Hello,

I am currently designing the DLPC910 platform and have two questions.

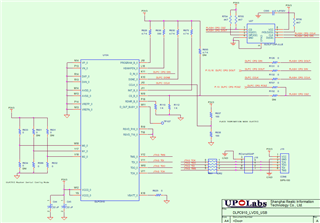

1. Due to the discontinuation of DLPR chips, the DLPC910 currently uses SPI FLASH as the configuration device. The schematic diagram I designed is shown below. Please help me check if there are any issues.

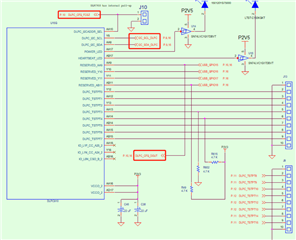

2. In DLPC910EVM, there are many TSTP signals, but in practical applications, these signals are not needed. In the following figure, can all signals except for those marked in red be omitted, that is, the pins are floating.

Thanks!

Sunny