Other Parts Discussed in Thread: DLP3021LEQ1EVM

Hi,

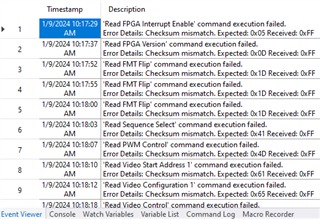

My EVM is not responding to both control program mode and fpga mode.

I am able to connect via GUI.

When i tried to change images via composer, it got crashed with below error:

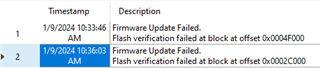

"Firmware update failed, flash verification failed at block at offset 0x00083000".

Even i tried to flash the default img, still same issue. Kindly help to fix this error.

Thank you

Kalaivani K