Hi TI expert

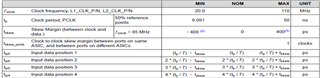

According the snla249 mentioned , there are three part of skew parameter defined .

1.Transmitter pulse variation.

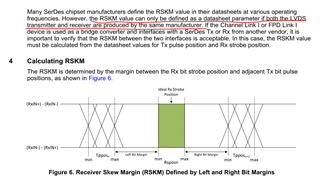

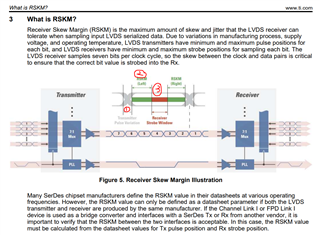

2.RSKM

3.Receiver Strobe Window.

Can you help to clarify in DS of DLPC231-Q1, tskew listed below represent to RSKM or strobe window?

BR Jingcheng