Hi TI expert

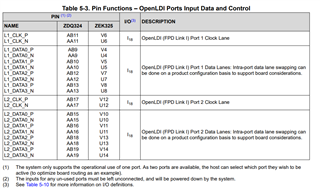

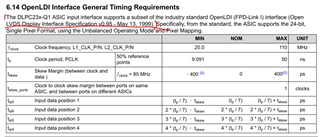

As the DLPC23x-Q1 ASIC input interface supports a subset of the industry standard OpenLDI (FPD-Link I) interface (Open

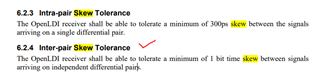

LVDS Display Interface Specification v0.95 - May 13, 1999), and in the v0.95 Spec shows , the receiver shall be able to tolerate a minimum of 1 bit time skew between independent differential pairs.

Can you explain how to implement this feature in IC side?

BR Jingcheng