Other Parts Discussed in Thread: DLP4710LC, , DLPA3005

Hello, TI expert

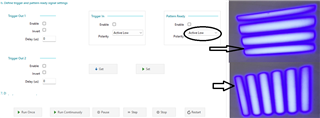

When we upgraded the 8.3.0 firmware, we found that when the pattern ready signal was set to high, the left and right sides could easily get out of sync when projecting the internal mode. When paused, the left pattern and right pattern may not come from the same pattern. This error occurs whether pattern ready is enabled or not. But it works well when the pattern ready signal is set to low. For firmware 8.1, there is no such exception.

Environment: dlpc3479+dlpa3005+dlp4710lc+pm1.

Thanks