Other Parts Discussed in Thread: DLP4620SQ1EVM, DLP4621-Q1, DLPC231-Q1

Tool/software:

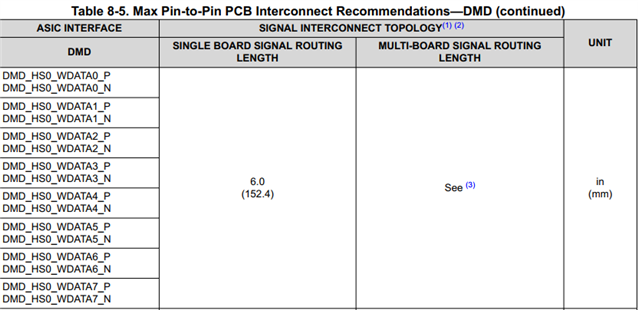

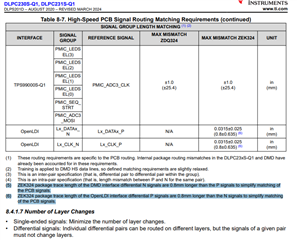

In DLPC231S-Q1 datasheet, there is a limitation of high speed data line.

The max pattern length is 152.4mm in case of single board.

Currently, in our design, those signal pattern length is little bit bigger about 10~20mm.

My question is that what I can do if display is not normal due to the pattern length.

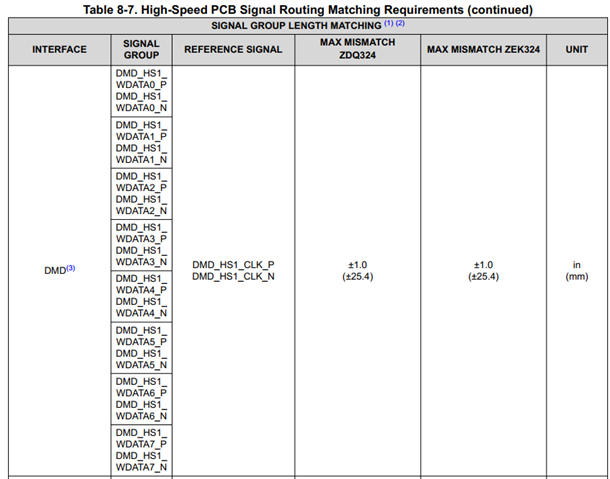

If intra patten lengths(for example clk line and data line) are adjusted almost same length, then maximum pattern length can be increased?