Tool/software:

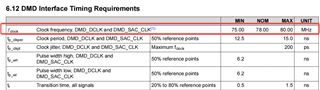

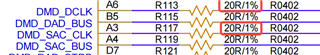

Hi,During the test of our DLPC120+DLP3030 system, RE did not meet the requirements (AV value of about 76MHz exceeded 3dB). After investigation, it was caused by the clock at the DMD interface. We have done shielding treatment for FPC cbale, but it still did not meet the requirements. In addition, we changed the resistance of DMD-CLK and DMD-SAC-CLK from 20 ohms (EVM resistance value) to 33 ohms and passed the test. However, please help to confirm whether increasing the resistance value has other effects.