Tool/software:

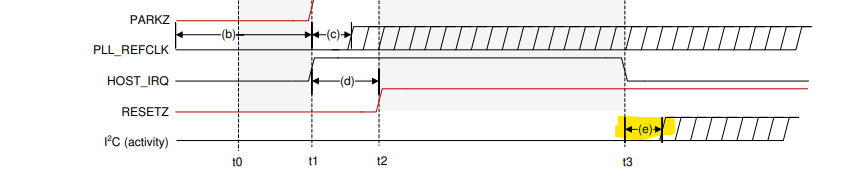

Regarding the timing of DLPC3435's HOST_IRQ and I2C, are there any timing regulations for the period from the falling edge of HOST_IRQ to the start of I2C?

I would like to know if there is a minimum required time regulation.

It is the time (e) in the diagram below.