Other Parts Discussed in Thread: DLP9500, , DLP650LNIR, DLPA200

Tool/software:

Hi, TI expert:

I use my own board design, the hardware architecture is FPGA+DLPC410+DLP9500。

We have adopted a new approach by flashing the firmware provided by TI into the flash memory. Currently, the DDC_Version returns 0, while previously, when using the DLPR410A, the DDC_Version was 7. We are unsure what the DDC_Version should be with this new approach and what the difference is between 0 and 7. Are there any important considerations?

We tested the PCB with the modified firmware using the same code previously used for DLPR410A testing and found the following issues:

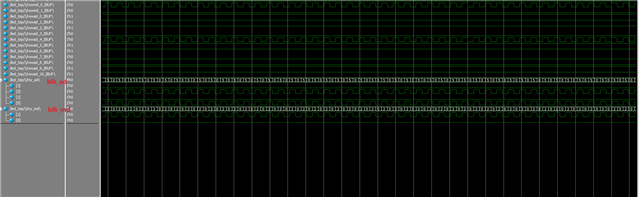

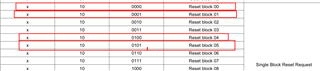

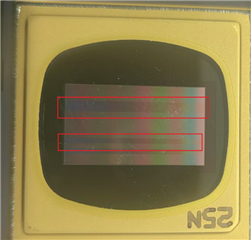

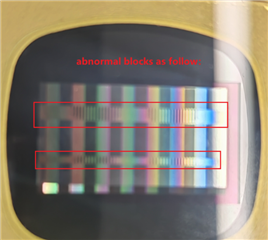

After powering on and completing initialization, approximately three blocks are malfunctioning, as shown in Picture1. These blocks do not behave as expected when displaying images on the DMD, as illustrated in Picture2. We monitored the rst_active signal and observed a 4.5 µs pulse, indicating it is functioning correctly. However, when switching images, these blocks still fail to respond.

Setting the pwr_float signal to low and measuring the AC17 pin of the DLPC410 on the PCB showed a high-level signal. Under normal circumstances, it should be floating, but there is no change in the DMD.

Could you provide any troubleshooting suggestions?

thank you very much!