Hello!

I'm working with the DLPC200 via SPI, and so far I've got robust communication with the DLP; I'm able to query version numbers, change the image order LUT, etc. Where I'm stuck is in loading a solution from the parallel flash that I've written (all via SPI).

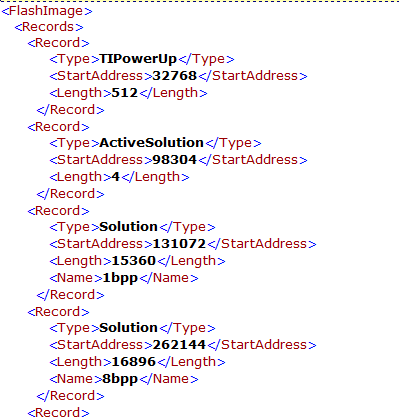

I'm able to write a 0x138000 byte solution binary file consisting on a single 8bpp image compiled using the X3 Control Software to the parallel flash using the low level 'Parallel Flash Download' commands (section 7.4.2 in the SPI Slave Interface Specification document). The response to the final packet indicates success, although it is different than the expected low level packet response (section 7), and appears to mention the number of bytes written.

I am loading the parallel flash starting at 0x00000000. When I attempt to load the solution from 0x00000000 using LoadSolutionFromFlash (section 6.50), bit 6 of Data[0] in the response (section 6) is set. Using GetExtendedPktFailReason (section 6.1), code 0x0006 is returned, indicating the solution offset address is invalid.

When I tried loading the parallel flash starting at 0x00001000, LoadSolutionFromFlash (using address 0x00001000) still fails, but GetExtendedPktFailReason gives code 0x0007, indicating that the flash is not programmed.

Before writing the flash, I issue a Parallel Flash Erase (section 7.5.1) command, to erase the region from 0x00000000 to 0x01000000. The response indicates success.

Before loading the solution from the flash, I issue a WriteImageOrderLUT (section 6.14) command to only display image 0, in case the DLP has trouble when non-existant images are referenced in the Image Order. The response indicates success.

Is there anything I'm doing incorrectly, or not doing?

Thanks!

-Matt