Hello,

I am reading the datasheet "System Power and Reset" of DLPC350. (dlps029c: P43)

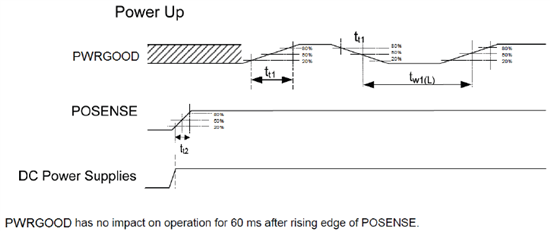

I have a confirmation about relationship between PWRGOOD and POSENSE.

Which is correct spec on power up sequence?

a) PWRGOOD must be high after more than 60msec after rising edge of POSENSE.

b) PWRGOOD must be high after rising edge of POSENSE.

There is no timing spec, but it has effect after more than 60msec.

c) You can PWRGOOD become high before rising edge of POSENSE.

But it has effect after more than 60msec after rising edge of POSENSE.

Best regards, RY

dlps029c:P43 System Power and Reset