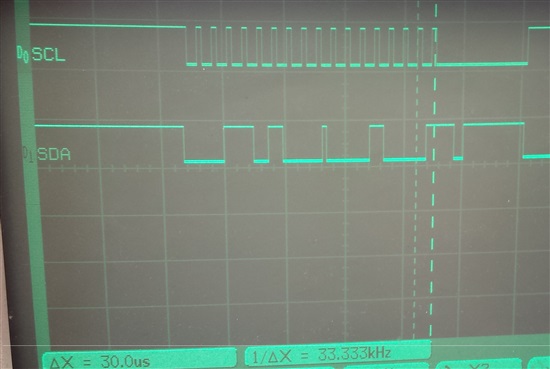

I try to read the registers via I2C after DLPC350 is booted but scl is sticked low after I send the sub-address. See the below figure. After the 8. (before the 9. Tact “acknowledge”) the SCL is sticked low. It has the same behavior with 100KHz .

The state is:

1)DLPC is booted

2) DMD schows the internal pattern (TI LOGO)

3) I2C_ADDR_SEL ist LOW