hi TI experts,

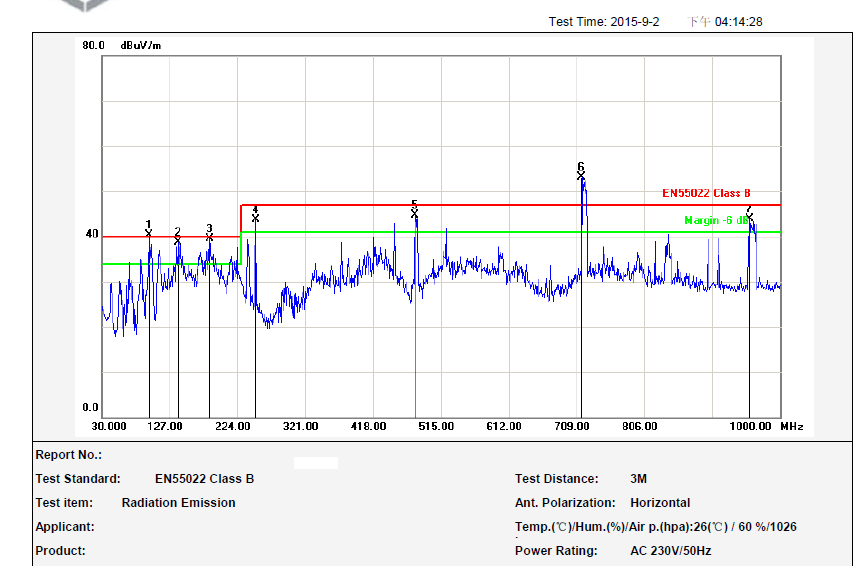

I have a product which is used a DPP6401chipset , i am meeting a trouble on EMI test without an available solution to fix it for 720MHZ emission ,i found it was

radiated out between DPP6401 to DMD(0.45) ,i has tried to debug the parameters of the oscillator R,C, add the bead cores or change the value on VCC

cicuritry of DMD&DPP6401,but no obvious effects . i found there was obvious effects when added bead cores on the trace between DPP6401 and DMD ,but the

720MHZ can't be under the spec yet . do you have any good ways to fix it well ?

thanks a lot .