Hi,

We have done a custom DLP board design with DLPC300 + DLP3000 chipset. I'd like to confirm a power-off timing requirement.

In a situation of system input power loss, we have designed so there is enough charge on the power rails to satisfy power-off sequence requirement by all devices:

- DLP3000 mirror parking of 500uS [ref. DLPC300 datasheet section 9.1.2]

- DMD Vbias/offset/reset settling within thresholds [ref. DLP3000 datasheet section 9.3]

The confusing part is on #2,

- DLP3000 datasheet rev. B says Vcc and Vref must held until Vbias/offset/reset are settled within thresholds

- DLPC300 datasheet rev. C Fig. 17 says Vcc18 must stay high for 100mS to satisfy the above requirement.

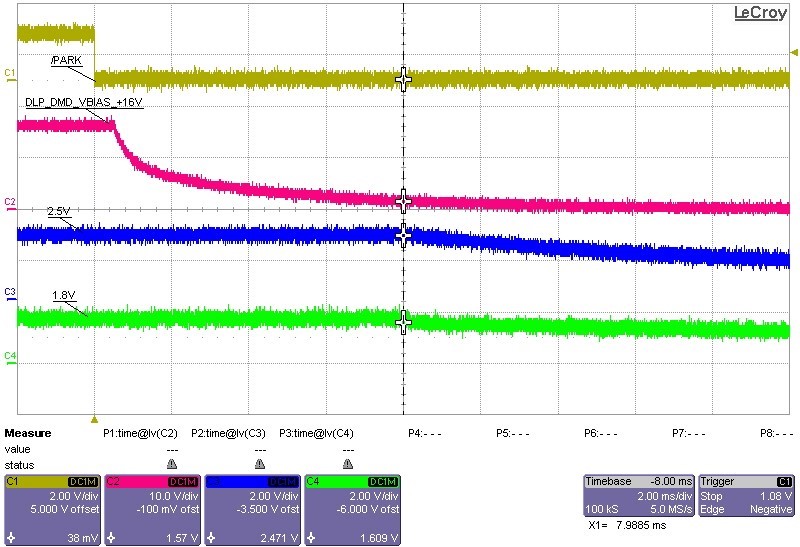

With our current DLP design, the DMD Vbias/offset/reset settle under threshold ~4.5mS after DMD_PWR_EN deassert. We hold Vcc18 for ~7.5mS. So the design satisfies DLP3000 datasheet. Do you see any design issues?

Is 100mS from DLPC300 datasheet a general suggestion? We don't want to add unnecessary rail capacitors due to limited board space.