Other Parts Discussed in Thread: DLP7000, , DLP7000UV

Tool/software: Code Composer Studio

Hi,

Our setup is as followed: (Virtex7, DLPC410, DLP7000)

https://e2e.ti.com/support/dlp/f/94/p/759718/2806469

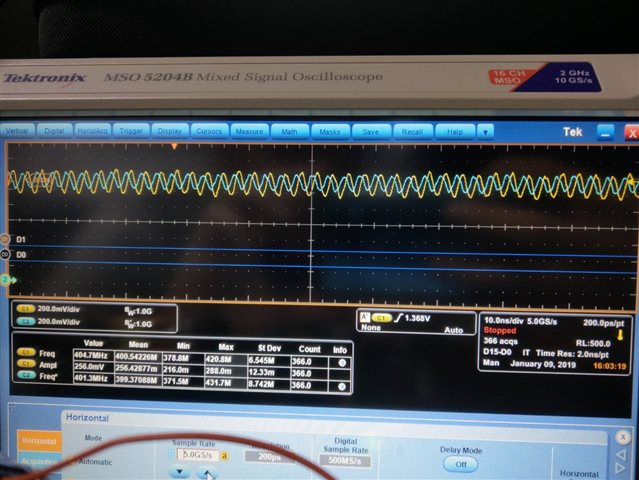

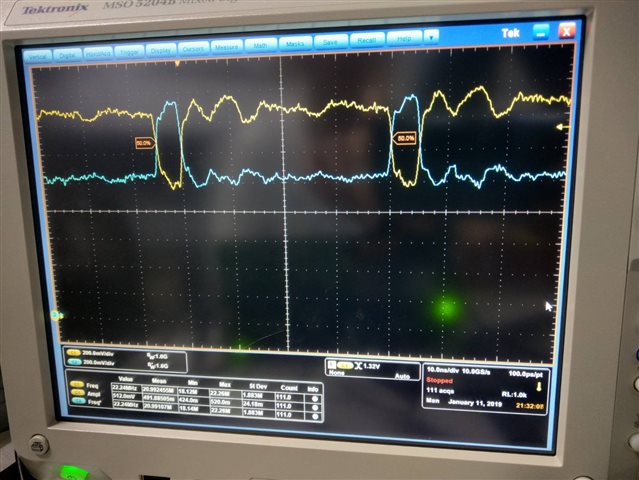

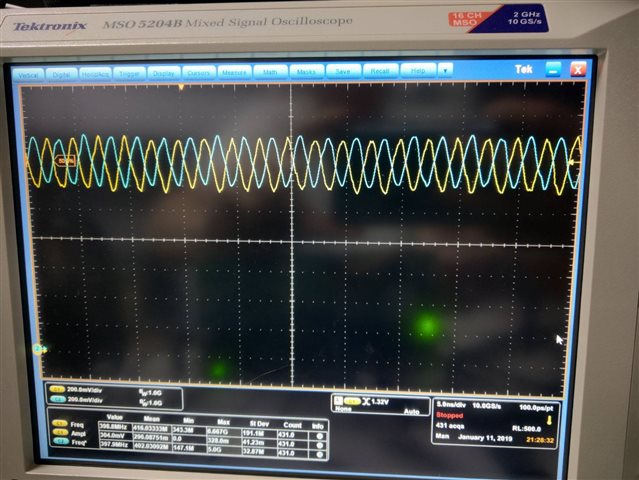

As we have resolved the previous problem, the DLPC410's initialization and calibration go successfully, and we can also retrieve the right DMD_TYPE and VERSION. However, the control outputs somehow couldn't get to the mirror, and I'll list some of our observation below:

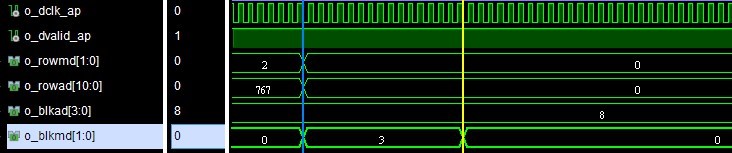

1. The RST_ACTIVE stays low even after we output BLK_MD = 11, BLK_AD = 1000, ROW_MD = 00, ROW_AD = 'd0, and other control signals (e.g. wdt_ena, rst2blkz, ns_flip ...) weren't toggled during the output.

2. ECP2_M_TP16 (Clock reset) stays high after initialization. We're not sure if this is normal and what causes this if it is not.

Thanks,

Justin