Other Parts Discussed in Thread: DLPC410

Hi,

In our application of FPGA driving DLPC910 and DMD module (DPL9000), We are facing an odd image-overlap on DMD.

Please allow me to explain what kind of image-overlap I had in my design.

Let's say I firstly display a square on DMD and then display a circle, the normal result is that only a circle should be observed on DMD.

But sometimes, I observed that square and circle are overlapped each other. I call this abnormal case image-overlap.

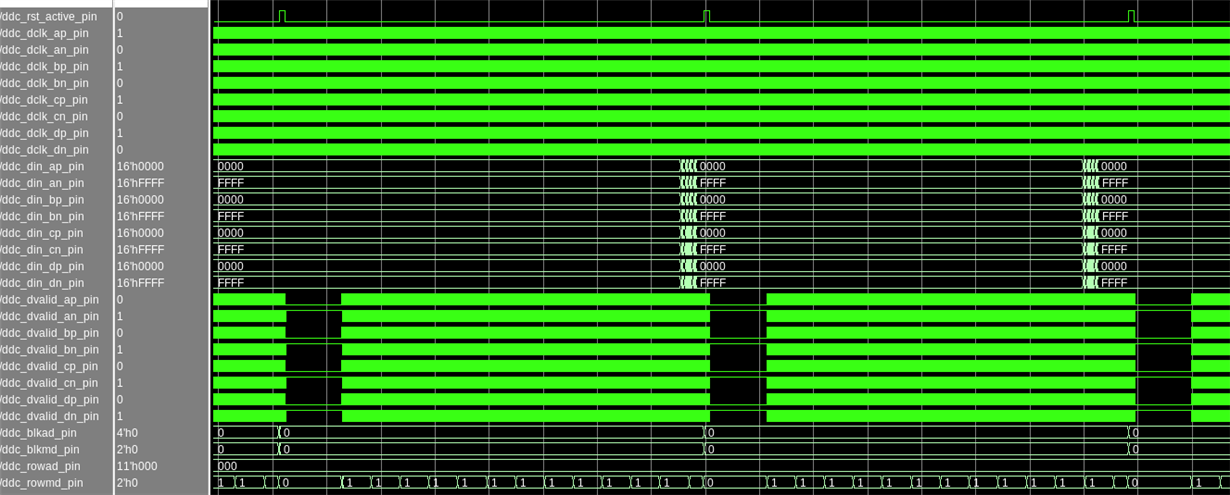

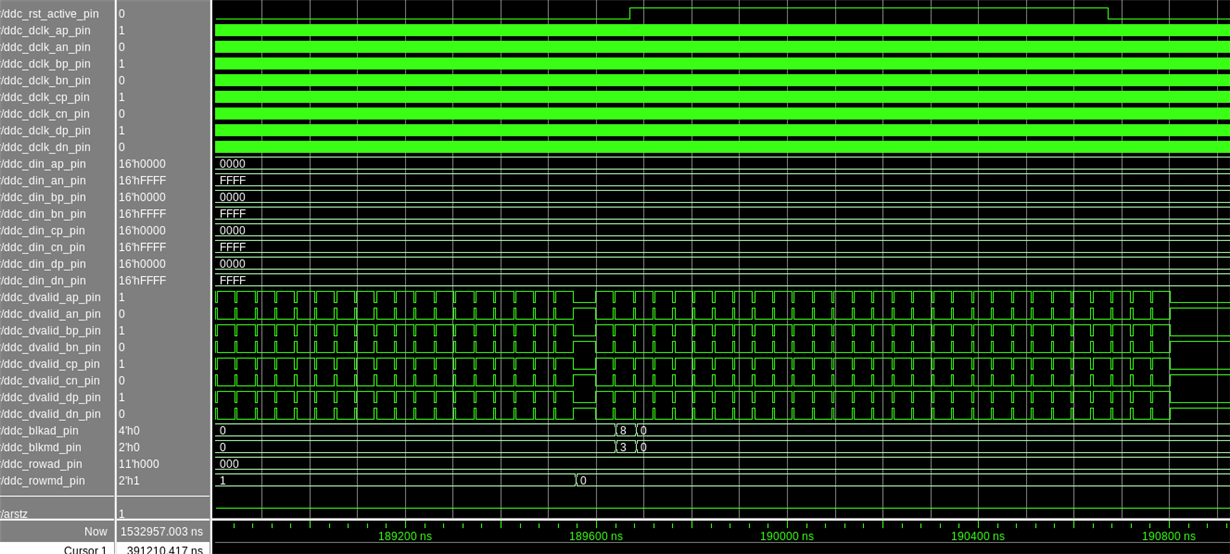

Below are the test results and observation I did

1. because I need to keep refreshing DMD by using different image, I don't know when image-overlap is going to happen.

2. Once image-overlap happened, I have to keep refreshing the image I want to display until it can be displayed on DMD correctly, which means I don't know when image-overlap will go away.

3. the first image after power cycle or DLPC reset is always good.

4. current walk-around is to do DLPC reset and LVDS training before I display image. <-- apparently it is not the correct way to display an image

I am in trouble with this issue, could you guys please to help?

If you guys want me to provide more details for troubleshooting, please let me know.

Thank you guys very much for any suggestion or information!!

Best!